@TOC

【FSMC】扩展外部 SRAM系列文章

前言

单片机内部通常集成了 SRAM 与 Flash 存储器,但容量相对有限。当项目需要更大的存储资源时,就需要通过外部接口扩展存储。由于我所使用的 STM32F407 系列芯片不支持外接 SDRAM,因此我选择通过 FSMC 接口来扩展外置 SRAM,以满足系统对更大存储空间的需求。

一、SRAM原理图介绍(IS62WV51216为例)

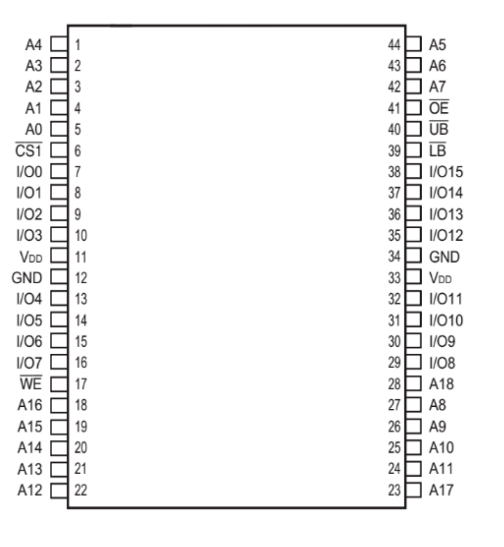

- A0--A18:地址输入

- I/O0--7:数据低八位

- I/O8--15:数据高八位

- CS1:片选信号,低电平有效

- OE:output enable ,输出使能,低电平有效

- UB:upper byte,高字节激活,低电平有效

- LB:low byte,低字节激活,低电平有效

- WE:write enable,写入使能,低电平有效

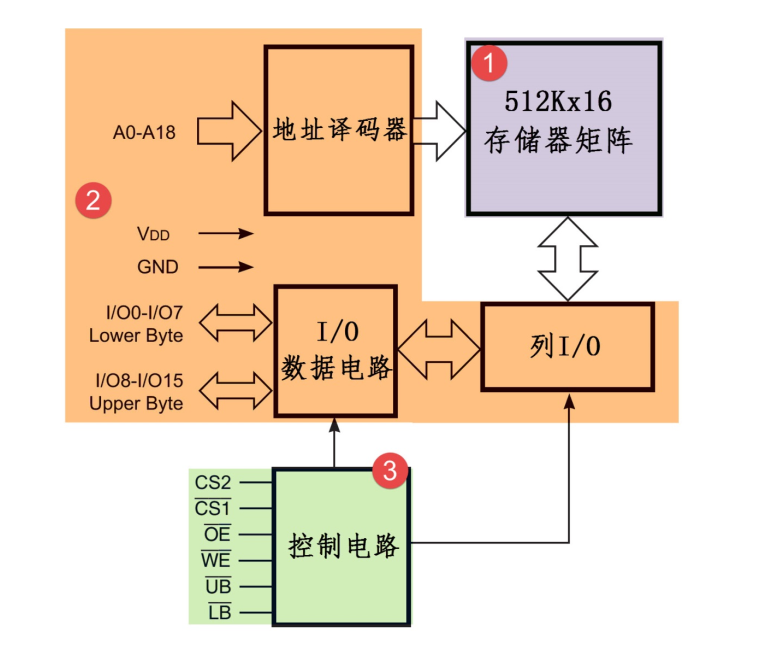

二、SRAM内部结构图解析

1.存储器矩阵

- 该存储器是512K * 16(bits),表示有512K个单元格,每个单元格可以放16个位的数据

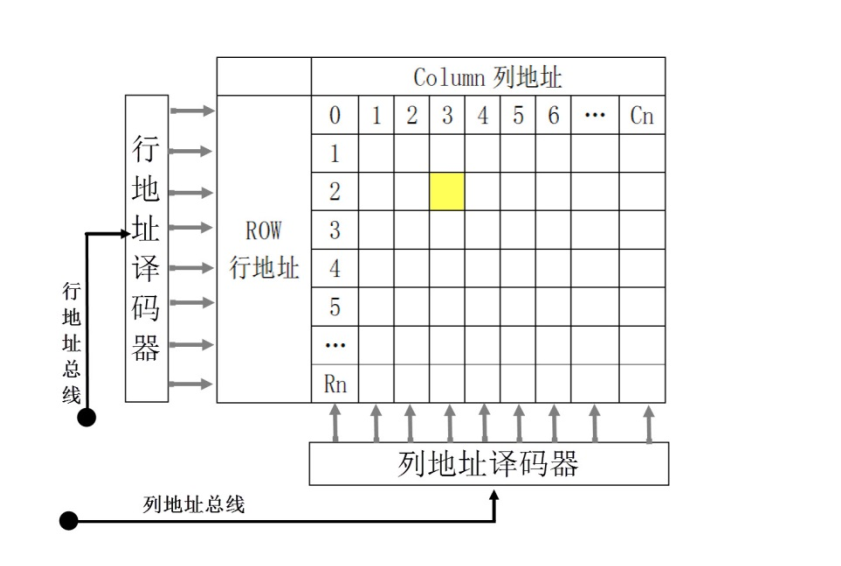

- 指定对应的行和列就可以指定对应的单元格,指定行的过程就是通过行地址总线输入,由行地址译码器选中对应的一行。列同理。

2.地址译码器、列 I/O 及 I/O 数据电路

地址译码器解释了为什么这个是512K个单元格?

地址译码器就是根据行地址总线和列地址总线进行选择对应的行或列,N条地址总线总共有2的N次方个信号线,512K = 2的8次方 * 1024,则有18根地址总线,由于该SRAM内存较小,没有列地址线,只有18根行地址线,每根行地址线对应16bits,也就是两个字节,解释了为什么他可以存放512K*16bits个数据。

有关I/O的则是与行地址总线,UB,LB有关了

- 16 位完整写入:当 UB# 和 LB# 同时为低电平时,高字节(I/O8–I/O15)和低字节(I/O0–I/O7)的通道都被激活,一次就能写入完整的 16 位数据。

- 仅高 8 位写入:当 UB# 为低、LB# 为高时,只有高字节通道被激活,低字节通道被屏蔽,数据只会写入 I/O8–I/O15。

- 仅低 8 位写入:当 LB# 为低、UB# 为高时,只有低字节通道被激活,高字节通道被屏蔽,数据只会写入 I/O0–I/O7。

3.控制电路

- 利用CS1和CS2可以把多个SRAM组合成一个更大内存的内存条

- 根据OE和WE可以控制读写过程

- 根据UB和LB可以控制数据宽度

三、SRAM读写流程

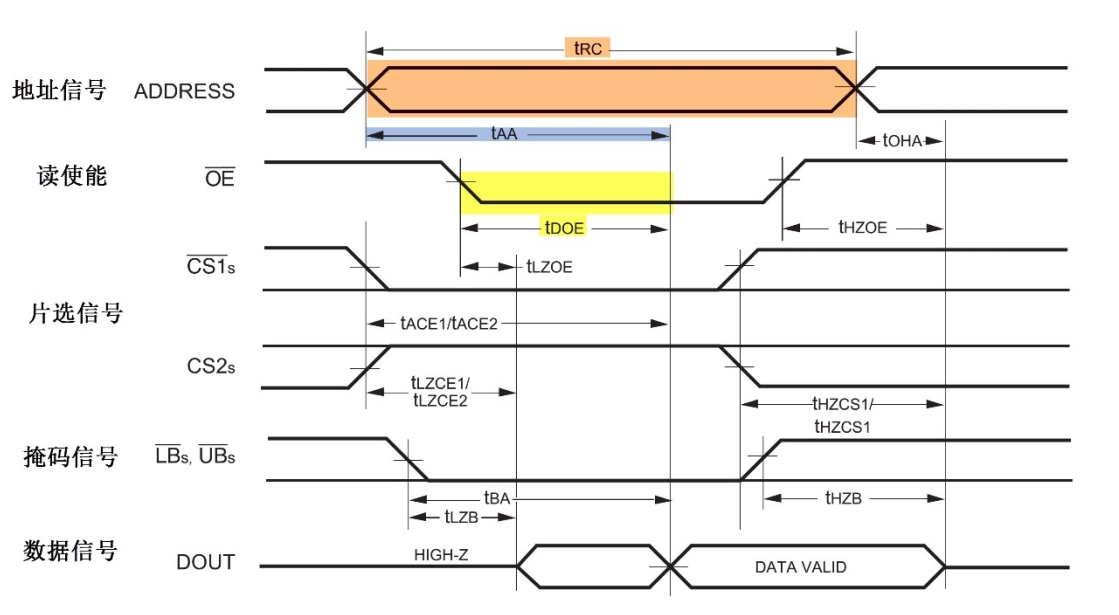

1.读的过程

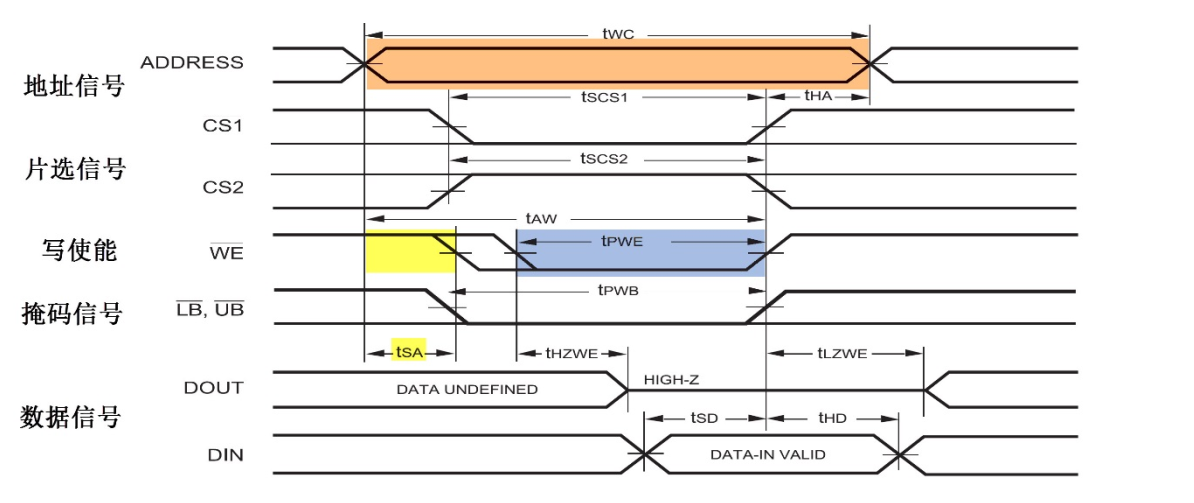

2.写的过程

3.概括介绍

- 主机根据信号地址线可以发送数据,选择要读写的存储器的目标地址

- 操作CS1/CS2来使能对应的存储器

- 如果想要写,就WE置低电平;如果想要读,就OE置低电平

- 接下来可以操作UB/LB来选择数据宽度

- 如果选择的是写,则主机通过信号线向存储器发送数据信号;反之同理。

注意:发送地址先于片选。这样可以保证存储器在被选中时,已经能识别到明确的目标地址,避免出现地址不稳定导致的错误寻址。

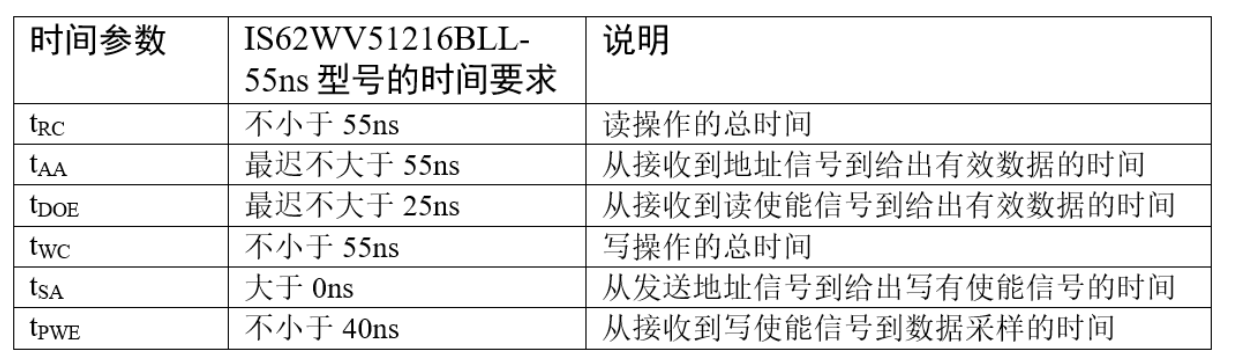

4.参数说明