引言Alphawave 告诉我们:“我能把数据搬得很快(PHY)”。但 Intel 和 AMD 最近甩出的王炸论文(UCIe-Memory)告诉我们:“我不只搬数据,我要消灭 DDR 和 HBM 的物理层!”

这不仅仅是带宽的提升,这是对冯·诺依曼架构中“内存子系统”的一次违章拆建。

01 UCIe 3.0:从“平面交通”到“立体折叠”

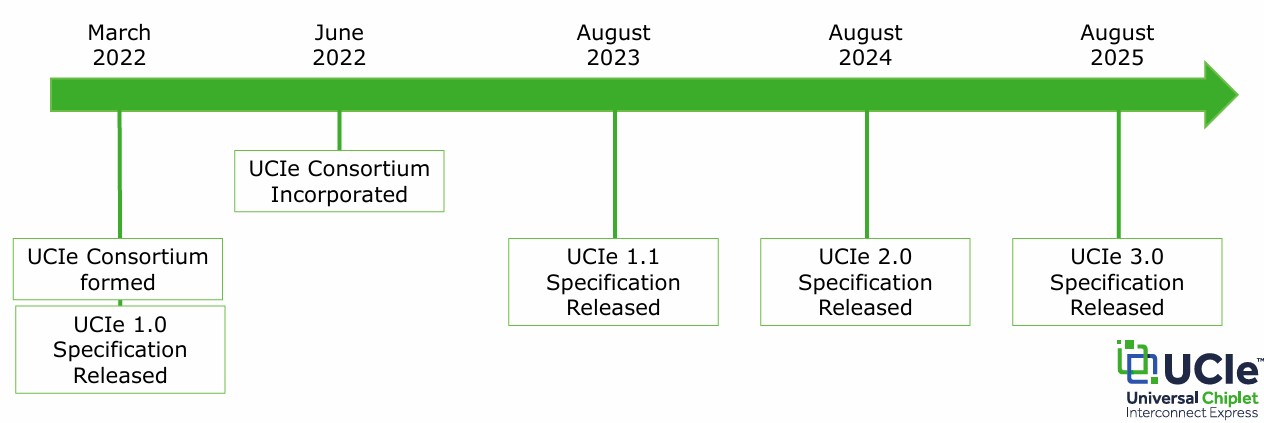

2025年8月,UCIe 3.0 规范正式发布。这可不是简单的版本号 +1,这是针对 AI 算力饥渴症的一剂猛药。

1. 速度翻倍:64 GT/s 的暴力美学

- Alphawave 的现状:致力于在先进工艺(3nm)下提供高质量的 24-64Gbps PHY。

- UCIe 3.0 标准:正式将单通道速率从 32 GT/s 拉升到了 64 GT/s。

- 老夫解读:这意味着在同样的芯片边缘(Shoreline)长度下,带宽直接翻倍。对于被“内存墙”逼疯的大模型训练芯片来说,这简直是救命稻草。

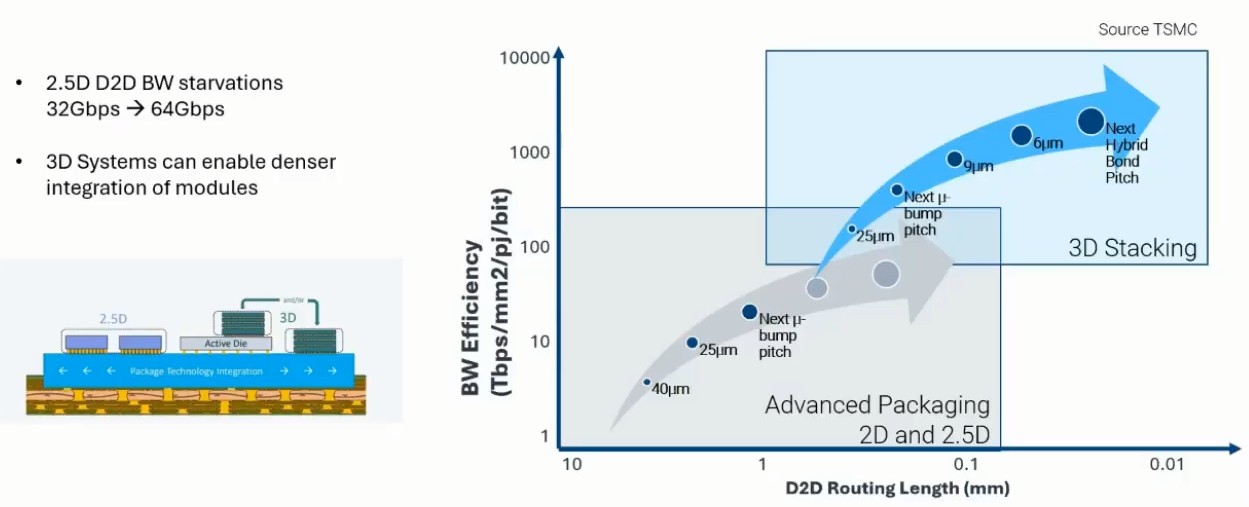

2. UCIe-3D:向 Z 轴要空间

这才是真正的杀手锏。UCIe 3.0 引入了 UCIe-3D,专门针对混合键合(Hybrid Bonding) 。

- Bump Pitch(凸块间距):从 2.5D 封装的 25-55微米,直接压缩到 < 10微米,甚至迈向 1微米。

- 带宽密度:相比 2.5D,3D 封装的带宽密度提升了 数个数量级。

- 对比:Alphawave 目前更多聚焦于 Chiplet 的水平互连(2.5D CoWoS 等)。而 UCIe 3.0 的野心是把 SRAM 直接“盖”在逻辑 Die 上,或者把两个逻辑 Die“脸对脸(Face-to-Face)”贴在一起,且标准通用化。

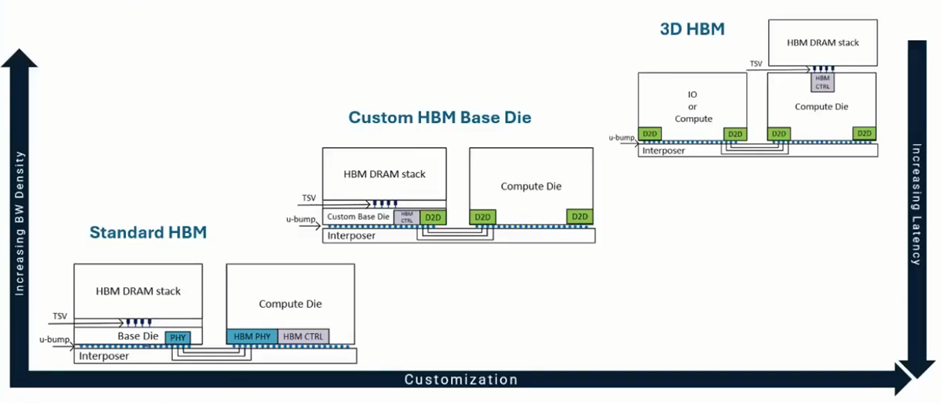

02 架构革命:UCIe-Memory —— 杀死内存物理层

核心痛点:

-

HBM:太贵,TSV 工艺复杂,CoWoS 产能是瓶颈。

-

LPDDR:太慢,位宽窄,PHY 占地面积大(模拟电路很难随制程微缩)。

革命性方案:用 UCIe 取代 DDR/HBM PHY他们提出了几种“离经叛道”的架构,这比单纯卖 IP 要深远得多:

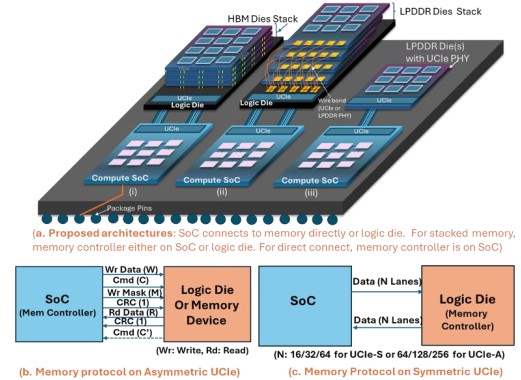

方案 A:“买办”模式(Logic Die Interposer)

-

架构:SoC (UCIe PHY) <--> UCIe Link <--> Logic Die <--> Standard DRAM

-

玩法:SoC 本身不再集成庞大的 DDR/HBM 控制器物理层,只保留极高密度的 UCIe。中间加一颗用成熟工艺(便宜!)制造的 Logic Die。这个 Logic Die 负责脏活累活(跑 DDR 协议)。

-

降维打击:

-

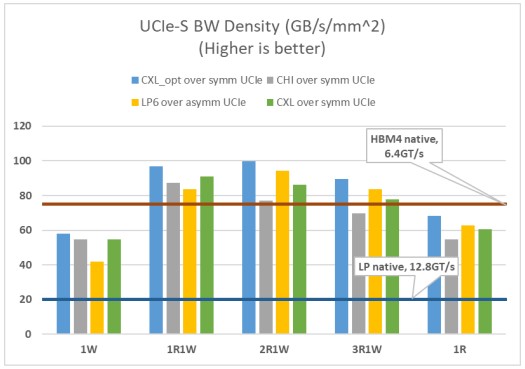

带宽密度:比传统 HBM4 提升 10倍。

-

功耗:降低 3倍。

-

成本:Logic Die 可以用 12nm/14nm 造,SoC 用 3nm 造,完美解耦。

方案 B:原生 UCIe 内存(Native UCIe DRAM)

-

玩法:直接让三星、海力士、美光把 DRAM 芯片上的 DDR 接口换成 UCIe 接口。

-

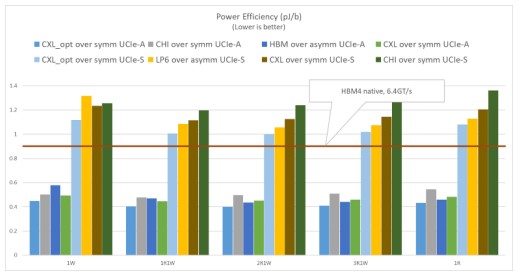

非对称设计:内存读写天生不对称(读多写少)。建议配置 74 Lane 的非对称 UCIe,按 3:2 或 2:1 分配读写带宽。这比 Alphawave 等厂商提供的标准对称 SerDes 更懂内存。

老夫点评:这比 Alphawave 单纯提供“连接管子”要高一个维度。这是在重定义“内存”在系统中的物理形态。如果这一步走通了,未来的 AI 芯片设计将彻底乐高化:“给我来两斤算力(Compute Die),再配三斤内存(UCIe-DRAM)。”

03 巨头的棋局:生态位的卡位战

除了 Alphawave 这种纯 IP 厂商,看看大佬们在干什么。

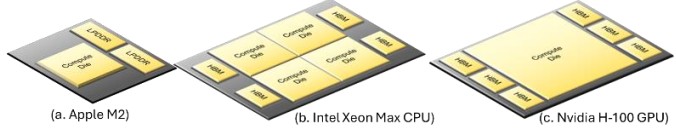

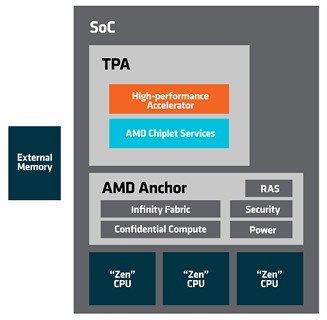

1. AMD:建立“帮派” (Chiplet Ecosystem)

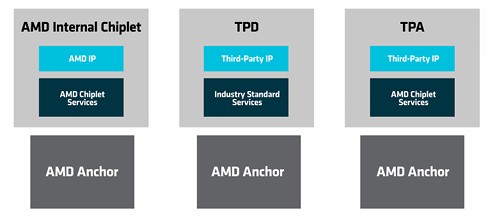

AMD 发布了详细的 Chiplet 生态白皮书。他们把 Chiplet 分成了三六九等:

- Internal Chiplets:自家兄弟,用私有协议(Infinity Fabric)。

- Third-Party Die (TPD):外人,必须讲普通话(UCIe)。

- Third-Party Adapted (TPA):通过 AMD 的桥接服务,让第三方 IP 也能接入 AMD 的锚点(Anchor)。

- 战略:AMD 在构建一个以自己为核心的“集散地”。他们不仅支持 UCIe,还在积极推动 iTPD (Intermediate Third-Party Die),这是一种过渡方案,允许 I/O Chiplet 先行解耦。

2. Intel (Foundry):我要做基建

Intel 的 18A 工艺平台明确将 UCIe 作为核心卖点。

- EMIB + UCIe:Intel 拥有目前最成熟的 2.5D 封装技术(EMIB),结合 UCIe,他们试图成为 Chiplet 时代的“富士康”。

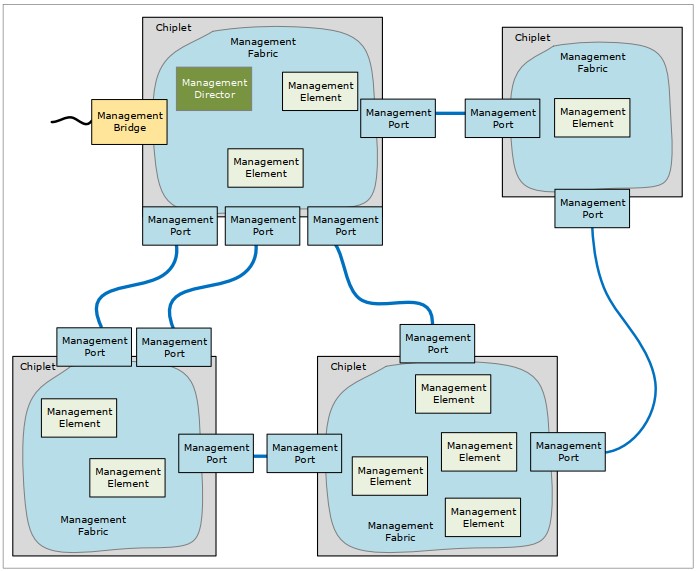

- 管理性 (Manageability):Intel 在 UCIe 3.0 中极力推动管理层协议。怎么发现坏掉的 Chiplet?怎么给没长大的 Chiplet 灌固件?这些“保姆级”功能是大规模量产的关键。

04 EDA 三剑客:卖铲子的艺术

当 Alphawave 在卖“金矿”(IP)时,Synopsys、Cadence 和 Siemens 在卖“挖掘机”。

- Synopsys:已经备好了 UCIe 3.0 IP(PHY + Controller)和 3DIC Compiler。他们的策略是“全家桶”,从架构探索到签核,让你没法拒绝。

-

Cadence:强点在于 System-Level。他们关注 Chiplet 拼装后的散热、供电和信号完整性。这在 3D 堆叠时代(UCIe 3.0)是比逻辑连接更要命的问题。

-

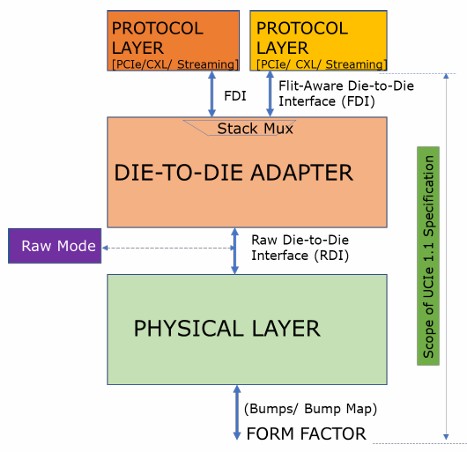

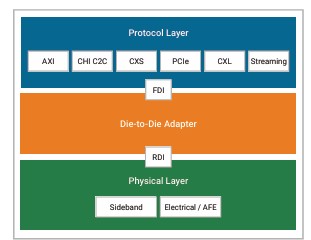

Siemens (Mentor):专注于 验证 (Verification)。UCIe 3.0 引入了复杂的边带管理(Sideband Manageability)和动态重校准。Siemens 的 VIP (Verification IP) 就是用来找 bug 的,确保你买来的 Alphawave IP 和 Intel CPU 能真的说上话。

05 总结与展望 or“终局推演”

对比 Alphawave 的 UCIe 方案与学术界/巨头的 Roadmap,我们可以看到清晰的分层:

-

物理层 (Physical Layer):Alphawave, Synopsys 等。

-

现状:卷速率(64G)、卷低功耗(pJ/bit)、卷工艺(3nm)。

-

评价:这是基础设施,也是红海。Alphawave 做得很棒,但这只是地基。

-

协议与架构层 (Protocol & Arch Layer):Intel, AMD等。

-

现状:卷标准、卷拓扑、卷内存语义。

-

评价:这是胜负手。特别是 UCIe-Memory,它试图把“内存控制器”从 CPU 里剥离出来,变成一个独立的 Chiplet。这会彻底改变 AI 芯片的成本结构(不再需要极其昂贵的 HBM,或者让 HBM 变得更便宜易用)。

-

系统层 (System Layer):UCIe 3.0。

-

现状:卷 3D 封装、卷管理性、卷可靠性。

-

评价:这是量产的关键。没有 Manageability,Chiplet 拼接就是开盲盒。

如果你关注 UCIe,不要只盯着 Alphawave 的眼图(Eye Diagram)看它又张开了多少。请密切关注“Logic Die”和“Active Interposer”的发展。 当内存控制器彻底独立,当 DRAM 开始原生说 UCIe 语言时,那个时刻,才是摩尔定律真正“复活”的时刻。

参考文献:

-

On-Package Memory with Universal Chiplet Interconnect Express (UCIe)

-

UCIe 3.0 Specification

-

AMD CHIPLET ECOSYSTEM

-

Alphawave Semi: Advancing AI

-

Synopsys: UCIe 3.0 Is Here