(存储器与CPU连接在后边)

译码驱动方式

一、线选法

地址线经过地址译码器转化为相对二级制对应的子线,每次选择一根子线上的所有位进行输出与写入。

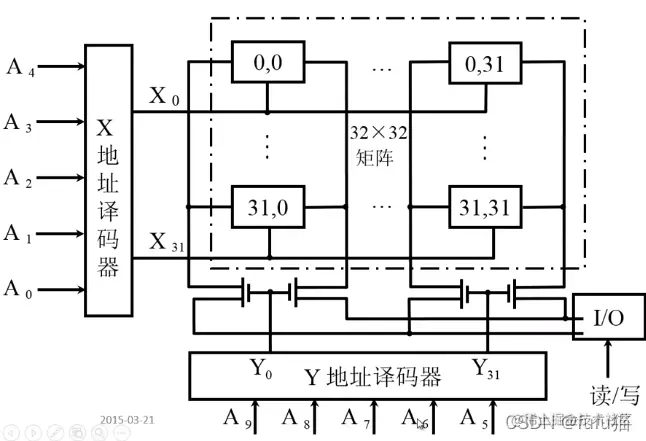

二、重合法****

![点击并拖拽以移动]() ****

****

增加了一排地址译码器,分别控制X线与Y线。每次选择一个存储单元,进行输入与输出。

三、对比

线选法结构简单,一般适用于容量不大的存储芯片 。而重合法存储结构复杂,芯片集成度高,存储容量大。

存储器与CPU连接

例题:

分析提米,数据线为8根则数据为8位。

第一步:画出系统程序区与用户程序区范围。

内存空间起始地址为0。

编辑

以上为系统程序区,系统程序不需要用户进行操作,故用ROM。(共4k空间)

题目中并没有给合适的芯片,所以就需要两片一样的2K×8位的ROM。

以下为用户程序区,需要进行操作读写,用RAM。

计算得知,需要空间为12K,选择3片一样的4K×8位的RAM。

地址为紧密排列,加一即可。

很容易看出,加粗的位置是不一样的。因此我们可以将此作为对应的片选信号。

但是ROM一样,这时只需要将A11单独拿出判断是RAM还是ROM就可以了。

Y0~Y3:A,B,C对应的二进制线路。

由图可知A15一直为低电平,所以将A15和MREQ与G2A和G2B连接。G1外接电源。

两个ROM串联。三个RAM串联。成功连接。