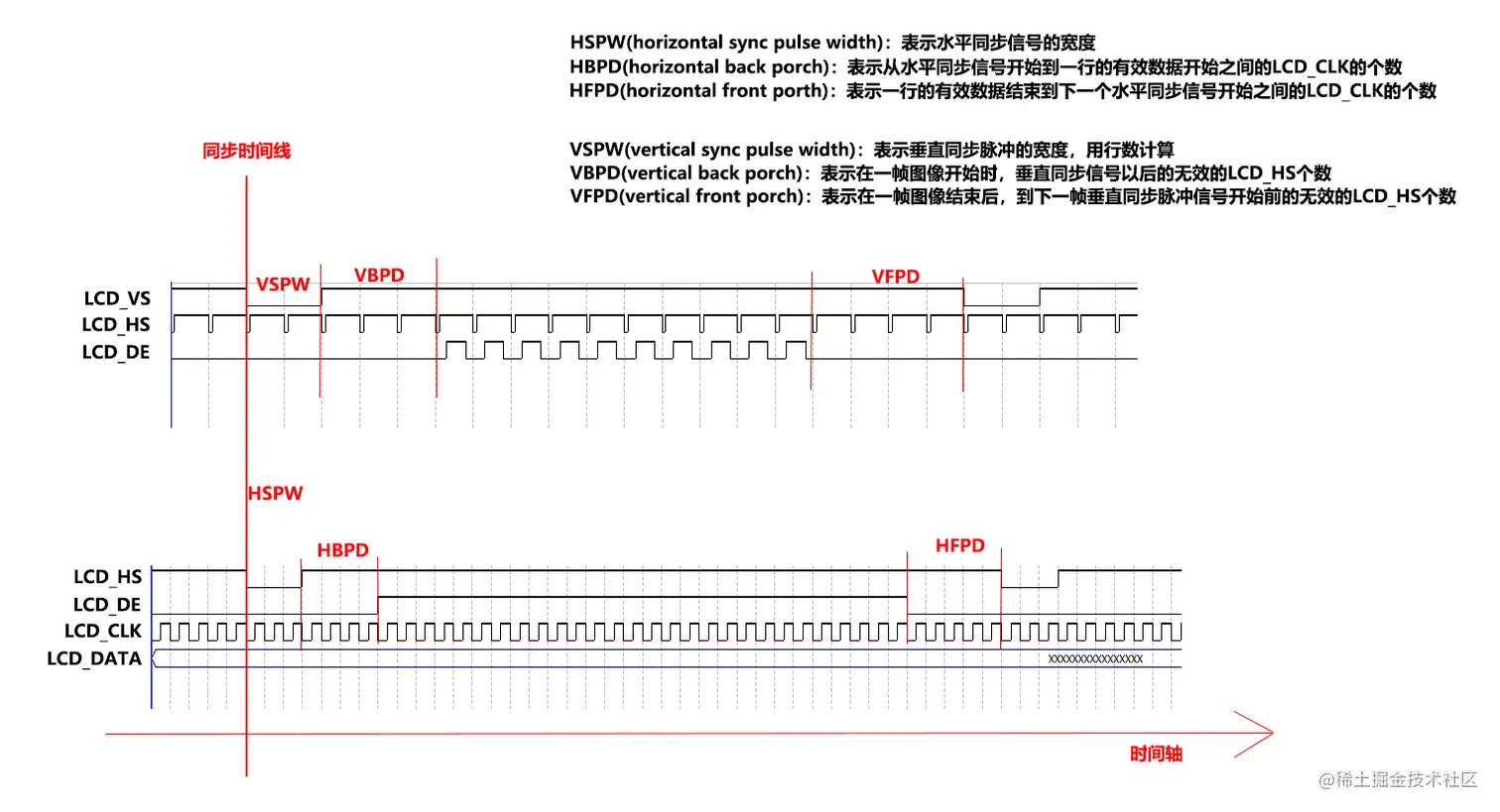

1. LCD时序图

2. fpga代码

module LCDTest(

input clk,

output lcd_clk,

output lcd_de,

output lcd_vs,

output lcd_hs,

output [15:0] lcd_data

);

`define H_FRONT 11'd40

`define H_SYNC 11'd48

`define H_BACK 11'd40

`define H_DISP 11'd800

`define H_TOTAL 11'd928

`define V_FRONT 11'd13

`define V_SYNC 11'd3

`define V_BACK 11'd29

`define V_DISP 11'd480

`define V_TOTAL 11'd525

reg [31:0] h_counter;

reg [31:0] v_counter;

reg [4:0] red;

reg [5:0] green;

reg [4:0] blue;

reg rgb_ready;

assign lcd_clk = clk;

always@(posedge clk)

begin

if((h_counter >= `H_SYNC + `H_BACK && h_counter < `H_SYNC + `H_BACK + `H_DISP) && (v_counter >= `V_SYNC + `V_BACK && v_counter < `V_SYNC + `V_BACK + `V_DISP))

begin

red = 5'b11111;

green = 6'b000000;

blue = 5'b00000;

rgb_ready = 1'b1;

end

else

begin

red = 5'b11111;

green = 6'b111111;

blue = 5'b11111;

rgb_ready = 1'b0;

end

end

always@(posedge clk)

begin

if(h_counter < `H_TOTAL - 1)

h_counter = h_counter + 1;

else

begin

if(h_counter == `H_TOTAL - 1)

begin

if(v_counter < `V_TOTAL - 1)

v_counter = v_counter + 1;

else

v_counter = 0;

end

h_counter = 0;

end

end

assign lcd_hs = (h_counter < `H_SYNC) ? 1'b0 : 1'b1;

assign lcd_vs = (v_counter < `V_SYNC) ? 1'b0 : 1'b1;

assign lcd_data = rgb_ready ? {red, green, blue} : 16'h0000;

assign lcd_de = rgb_ready ? 1'b1 : 1'b0;

endmodule