本文已参与「新人创作礼」活动,一起开启掘金创作之路。

建议有一定C基础的看,因为下面知识中,我省略了许多和C相同的内容。

当你看完下面内容后,应该就可以看懂一些基本的用Verilog语言编写的组合和数字电路了。

1.Verilog的数据类型

寄存器、线网数据类型和参数数据类型。真正在数字电路中起作用的数据类型是寄存器类型和线网数据类型。

1.1.寄存器数据类型

只能在always语句和initial语句等过程语句中赋值。它的缺省值(默认值)为x。

在实际数字电路中,如果该过程语句描述的是:

时序逻辑,则该寄存器变量对应为寄存器。

组合逻辑,。。。。。。。。。。硬件连线。

不完全组合逻辑。。。。。。。。寄存器。

![点击并拖拽以移动]()

1.2.线网数据类型

表示Verilog结构化元件间的物理连线,他的值由驱动元件的值决定。

![点击并拖拽以移动]()

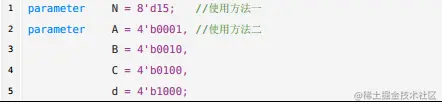

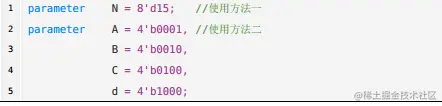

1.3参数数据类型

参数其实就是一个常量,通常出现在module内部,它可以再编译时修改参数的值,所以常用于一些参数可调的模块中,

Notice:参数的定义是局部的,只在当前模块中有效。

![点击并拖拽以移动]()

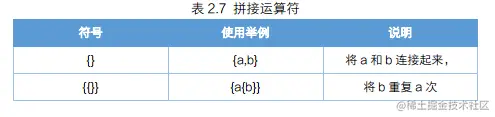

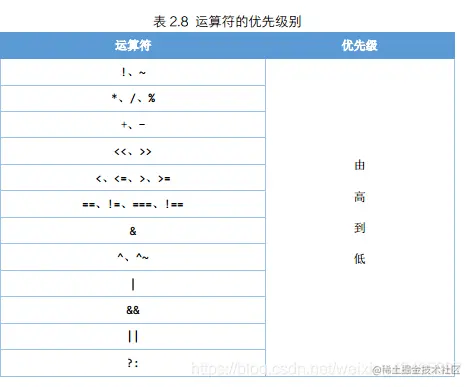

2.Verilog的基本运算符

![点击并拖拽以移动]()

![点击并拖拽以移动]()

![点击并拖拽以移动]()

二、Verilog基础语法

可综合:编写的Verilog代码能够被综合器转化成相应的电路结构。

不可综合:无法综合成实际的电路。我们可以用它来仿真、验证我们描述的数字硬件电路。for语句就不行

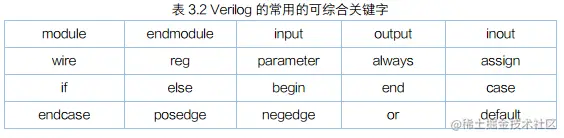

1.1常用可综合的关键字

![点击并拖拽以移动]()

always:过程赋值语句

assign:连续赋值语句

begin与end成对使用,相当于C语言的大括号。

case、endcase和default成对使用相当于C语言中switch

posedge(上升沿触发)、negecase(下降沿触发)和or这三个关键字和alaways关键字联合使用,posedge or negecase是既有上升沿又有下降沿。

always的两种用法

组合电路:

always @ (*)

begin

end

在组合电路:always@(*)表示输入有一个输入信号变化就会执行always里面的begin

时序电路

例:always @(posedge CLK_50M or negedeg RST_N)

begin

end