1. 物理单元

- GPC 图形处理集群,其中拥有多个TPC

- TPC 纹理处理集群,其中拥有多个SM

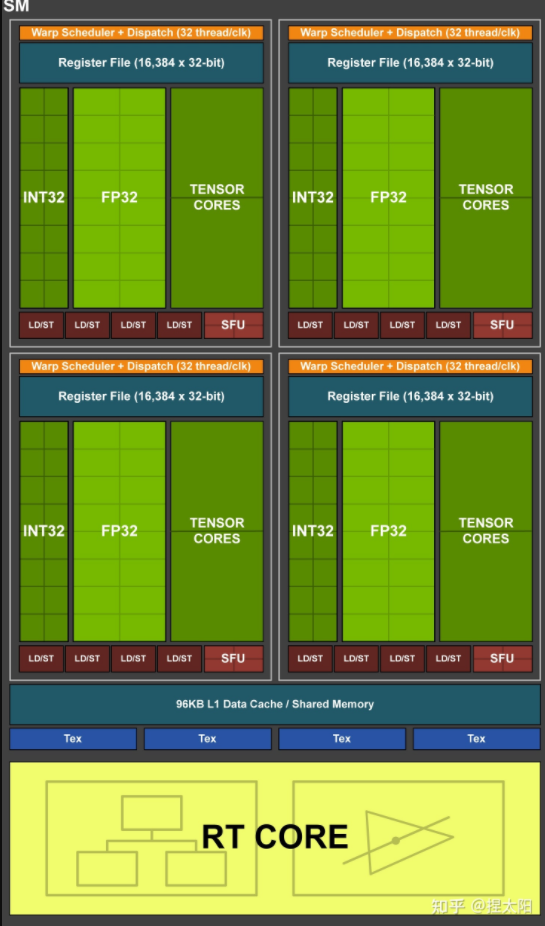

- SM(streaming multiprocessor) 流式多处理器,它包含若干调度器(Warp)、计算核心、寄存器、L1Cache、内存传输等结构

- Warp 调度器,其拥有软件意义和物理意义,存在于SM中的每个处理块中。每个调度器支持32路(32SP)的SIMT。

- Core 包含浮点核心、整数核心、Tensor核心等。

- Core与Thread(SP)并不是一一对应的。

- Warp实现的多Thread并行在物理上并非于一个cycle发出。Warp的32Thread于4个cycle全部发出。每个指令执行需要1个cycle,但具有4个cycle周期。

- Tex Texture 纹理访问

- TensorCore 能通过简洁指令执行矩阵运算的核心

- LD/ST 加载和存储单元

- SFU (Special Function Unit)特殊函数计算单元,执行插值运算等特殊运算。

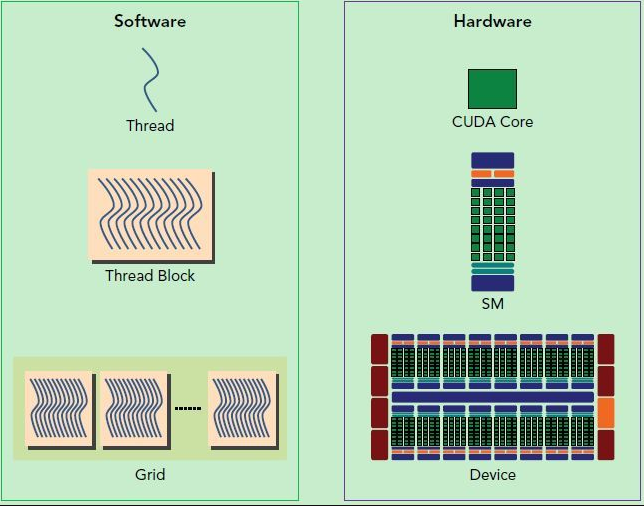

2. 软件单元

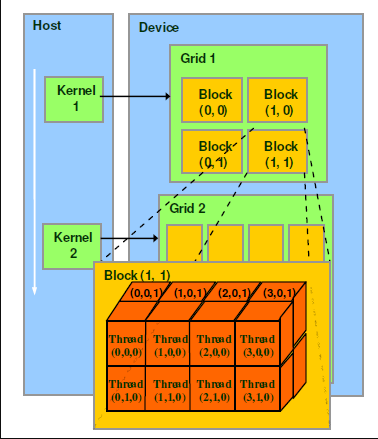

- thread: 一个CUDA的并行程序会被以许多个thread来执行。

- block: 数个thread会被群组成一个block,同一个block中的thread可以同步,也可以通过shared memory进行通信。

- grid: 多个block则会再构成grid。

3. 调度器(Warp)

调度器硬件(Warp)是存在于SM中的调度单元。调度器掌管着软件模型block和trhread级别的运行。具体的软硬件概念对应关系见右图。

硬件SM中每个block存在一个硬件warp。每个物理warp可调度32个线程。

虽然每个block没有32个硬件core存在,但是warp会以8或其他stride发射core命令。同样的虚拟化视角,每个硬件SM也会同时保持多个软件warp(可能有64个软件warp)。同一个硬件block中的软件warp能共享sharedmemory资源等。

多个软件warp存在于一个硬件block上。在软件层面,这些软件warp被绑定组成一个软件grid。