计算机组成-2.指令系统

分类

- CISC

- CISC是复杂指令集CPU,内部为将较复杂的指令译码,也就是指令较长,分成几个微指令去执行,正是如此开发程序比较容易(指令多的缘故),但是由于指令复杂,执行工作效率较差,处理数据速度较慢。例如intel和AMD的x86架构的CPU。

- RISC

- RISC是精简指令集CPU,指令位数较短,内部还有快速处理指令的电路,使得指令的译码与数据的处理较快,所以执行效率比CISC高,不过,必须经过编译程序的处理,才能发挥它的效率。例如ARM和MIPS架构的CPU。

x86体系结构(复杂指令集)

指令结构

- 类别

- 运算类指令

- 逻辑运算和移位指令

- 算术运算指令

- 完成加、减、乘、除等算术运算

- ADD指令(加)

格式:ADD DST, SRC 操作:DST←DST+SRC

ADC指令(带进位的加)

格式:ADC DST, SRC 操作:DST←DST+SRC+CF

INC指令(加1)

格式:INC OPR 操作:OPR←OPR+1

- 传送类指令

- 把数据或地址传送到寄存器或存储器单元中

- 格式:MOV DST, SRC 操作:DST←SRC

MOV EBX, 40 直接给出操作数

MOV AL, BL 给出存放操作数的寄存器名称

MOV ECX, [1000H] 给出存放操作数的存储器地址

MOV [DI], AX 给出存放“存放操作数的存 储器地址”的寄存器名称

- 转移类指令

- 作用

- 说明

- 根据是否有判断条件,分为无条件转移指令和条件转移指令两大类

- 根据转移目标地址的提供方式,可分为直接转移和间接转移两种方式

- 格式

- 控制类指令

- 运行结果

- 改变通用寄存器的内容, 如 ADD AX, DX

- 改变存储器单元的内容 如 MOV [10H], CX

- 改变标志位 如产生进位

- 改变指令指针 如 JMP [BX]

- 改变外设端口的内容 如访问显示端口

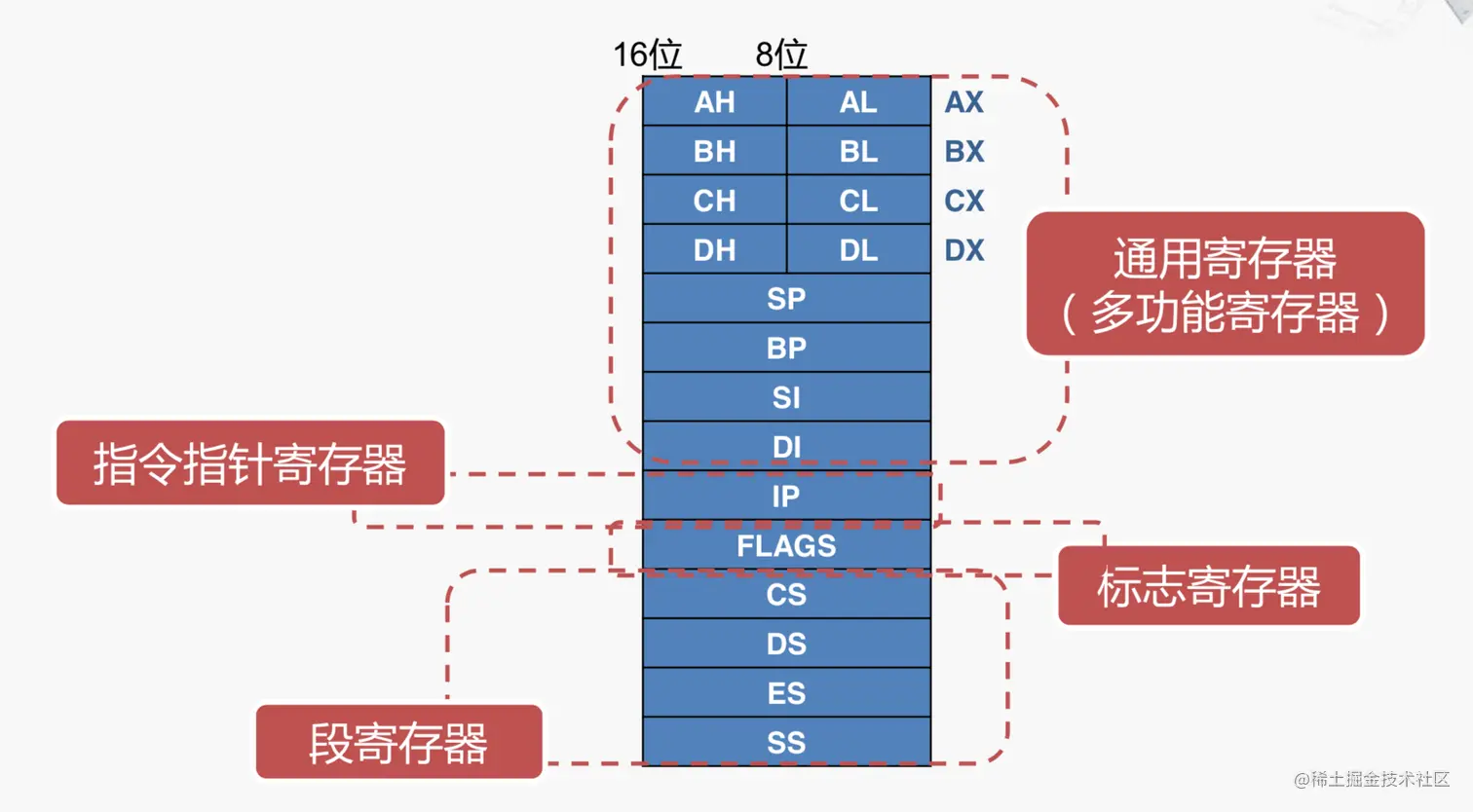

8086

- 特点

- 内部的通用寄存器为16位 既能处理16位数据,也能处理8位数据

- 对外有16根数据线和20根地址线 可寻址的内存空间为1MByte(2^20) 按字节编址

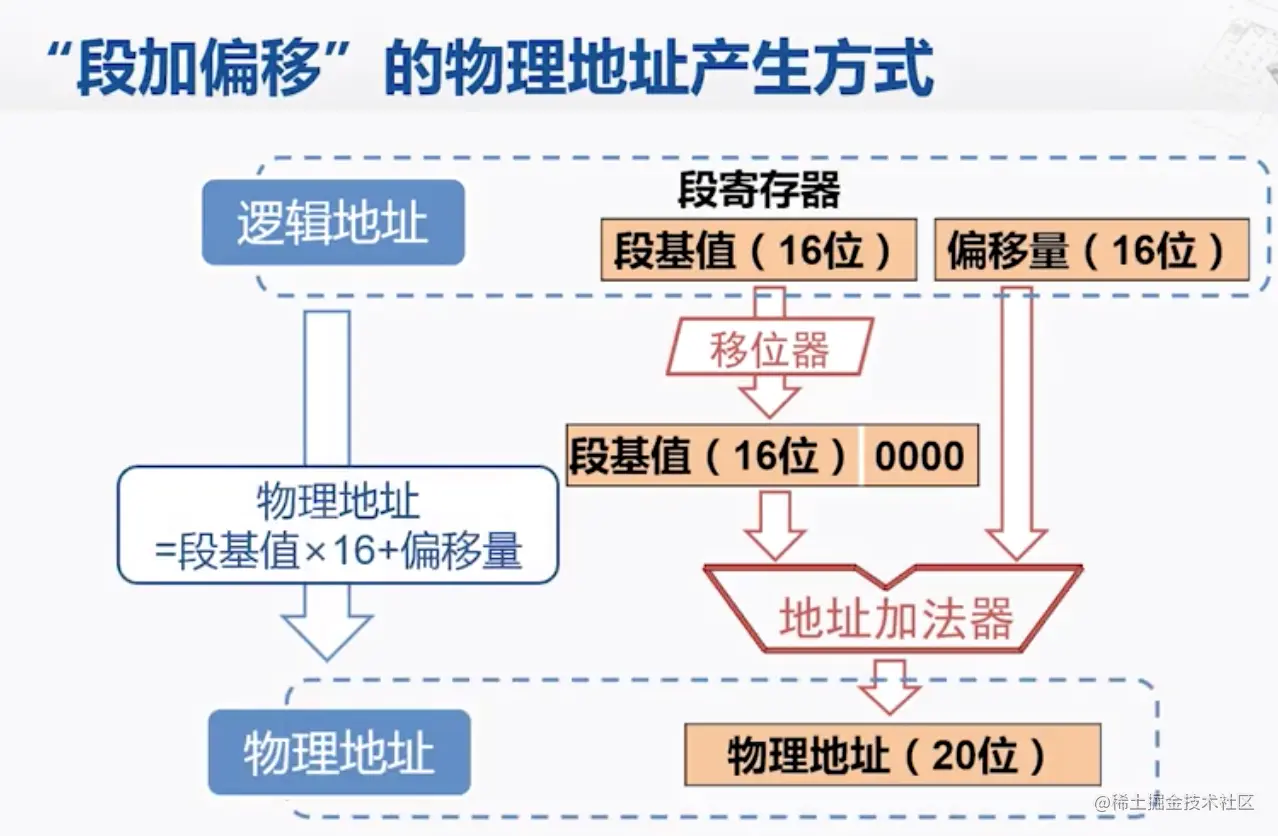

- 物理地址的形成采用“段加偏移”的方式

- 指令的寻址

- 实模式:CS:IP

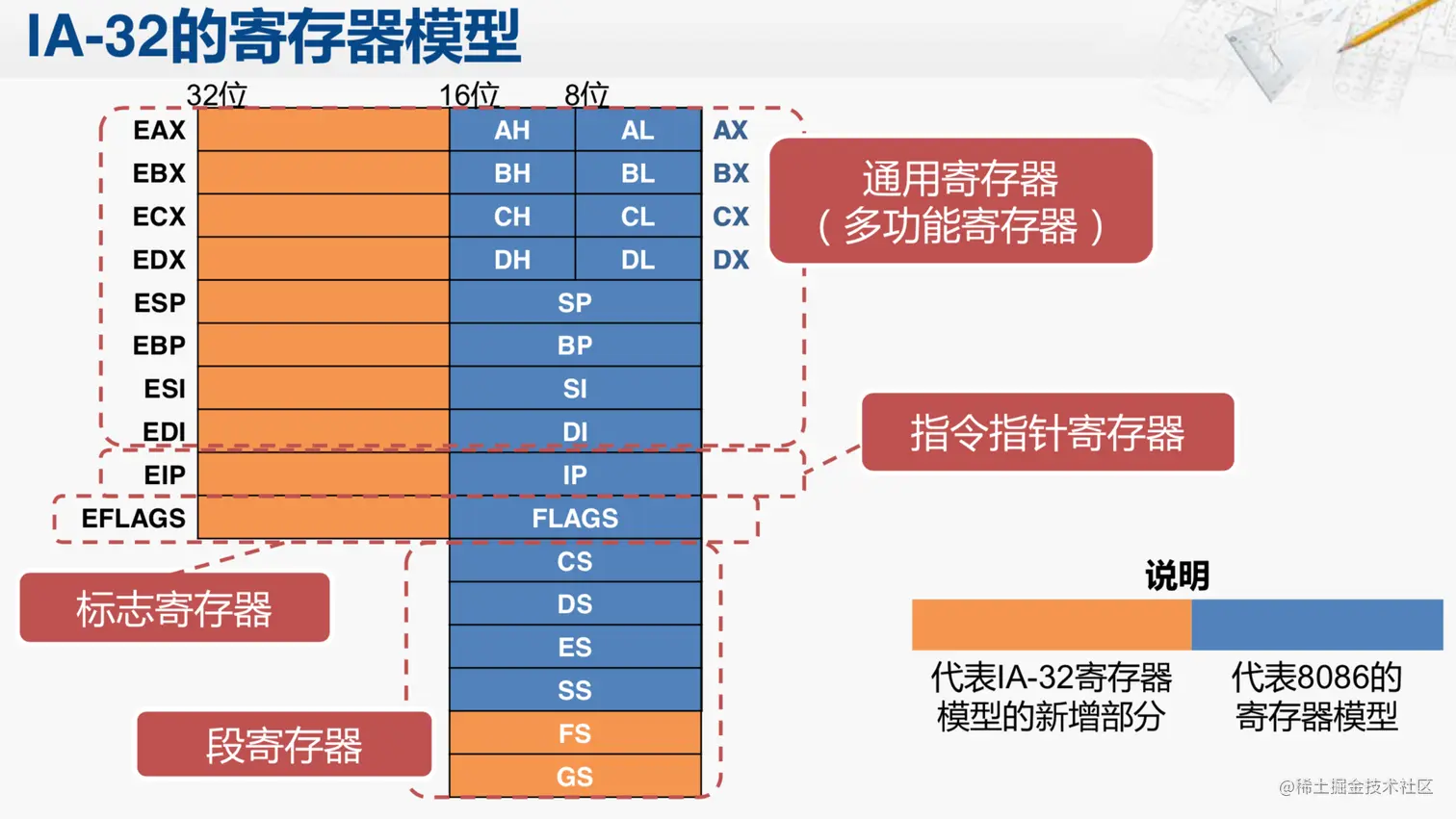

- 寄存器模型

- 数据寄存器

- 均为16位寄存器

- 每个16位寄存器都可分为两个8位寄存器使用

- 适用大多数算术运算和逻辑运算指令

- 标志寄存器

- 标志位

- FLAGS寄存器中包含若干标志位

- 标志位分为两大类:状态标志和控制标志

- 状态标志

- 反映CPU的工作状态

例如:◦ 执行加法运算时是否产生进位 ◦ 运算结果是否为零

- 控制标志

- 对CPU的运行起特定控制作用

例如:◦ 以单步方式还是连续方式运行 ◦ 是否允许响应外部中断请求

- 指令指针寄存器IP(Instruction Pointer)

- 保存一个内存地址,指向当前需要取出的指令

- 当CPU从内存中取出一个指令后,IP会自动增加,指向下一指令的地址(注:实际情况会复杂的多)

- 程序员不能直接对IP进行存取操作

- 转移指令、过程调用/返回指令等会改变IP的内容

- 段寄存器(Segment Register)

- IP寄存器的寻址能力: 216=65536(64K)字节单元,8086对外有20位地址线 寻址范围:2^20=1M字节单元

- 与其它寄存器联合生成存储器地址

- 物理地址 =段基值×16+偏移量

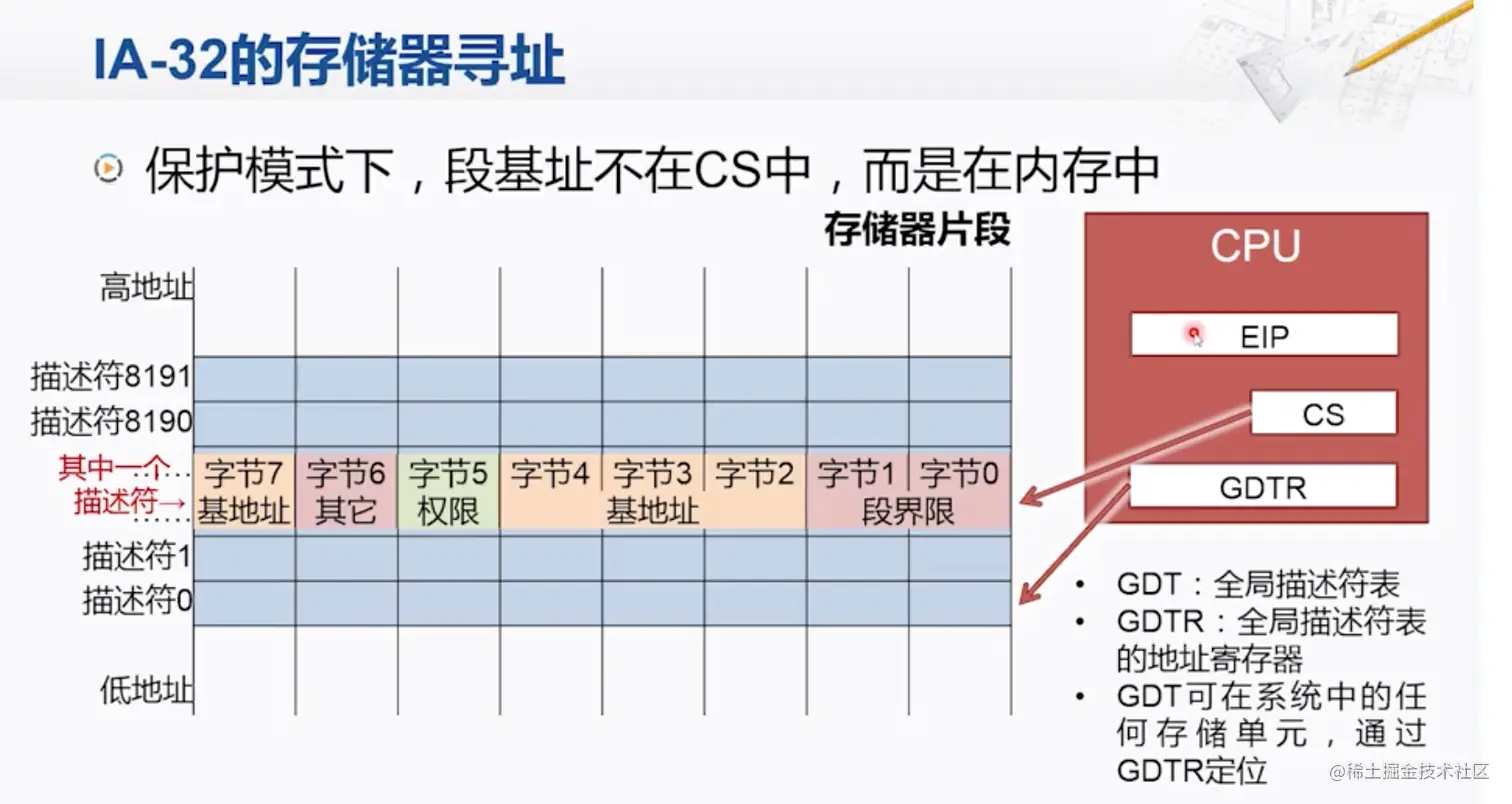

80386

- 特点

- 支持32位的算术和逻辑运算,提供32位的通用寄存器

- 地址总线扩展到32位,可寻址4GB的内存空间

- 改进了“保护模式”(例如,段范围可达4GB)

- 增加了“虚拟8086模式”,可以同时模拟多个8086微处理器

- 指令的寻址

- EIP寄存器的寻址能力:2^32byte;地址总线扩展到32位,可寻址4GB的内存空间。是一样的

- 保护模式下逻辑地址写成CS:EIP的形式,但物理地址的产生方式已经与实模式不同了

- 段基址不在CS中,而是存放在内存中

- CS寄存器的内存+GDTR寄存器的内容得到一个地址,用这个地址去访问存储器,取出这个描述符,再把描述符的第2、3、4、7字节的基地址提取出来,和指令指针寄存器EIP的内容进行组合,得到想要的存储器地址,用这个地址去访问存储器,得到想要的指令编码。

- 寄存器模型

x86-64

MIPS体系结构(精简指令集)

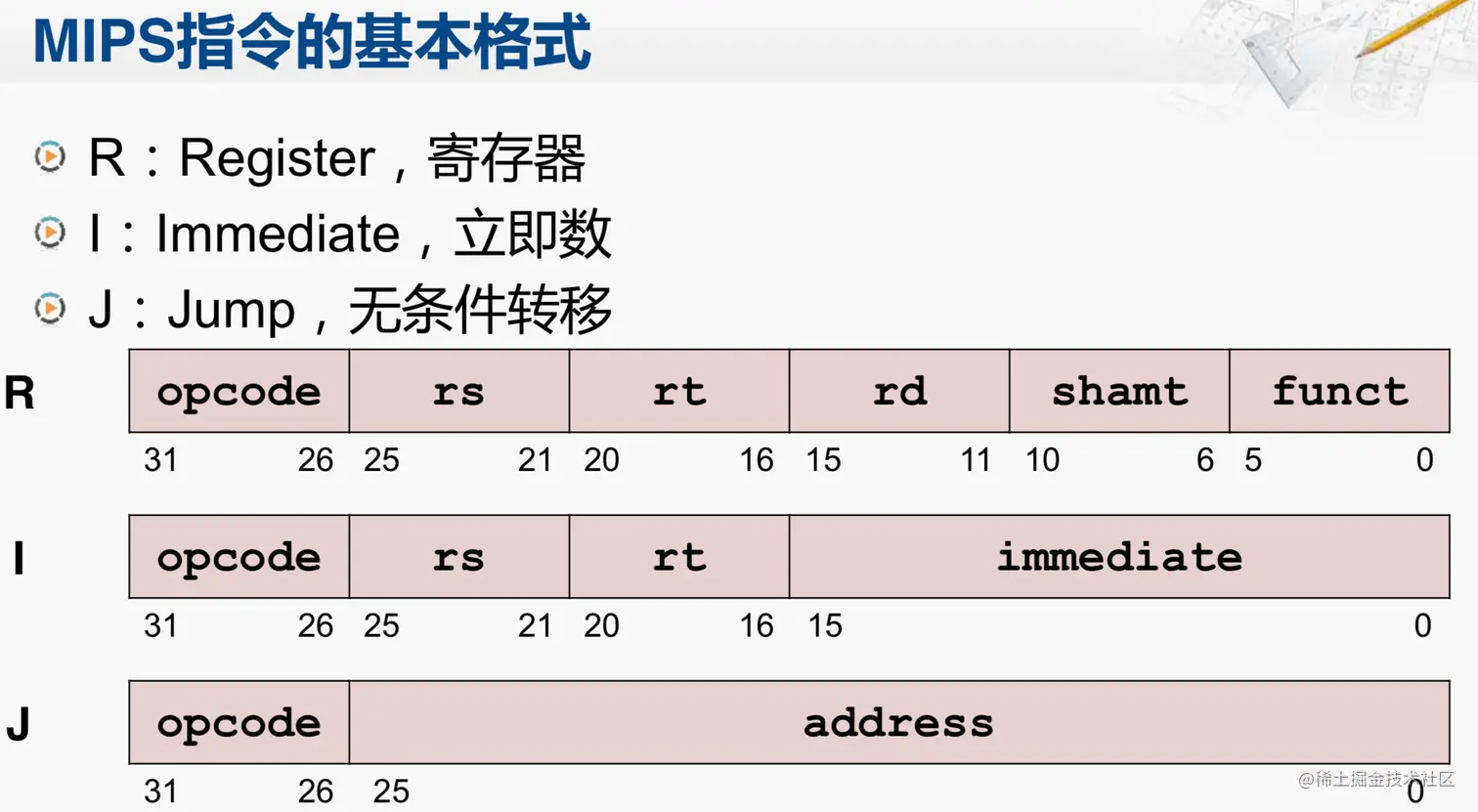

指令结构

- 基本格式

- 类别

- R/I/J

- 按功能分类

- 运算 指令

- 算术运算

- add rd,rs,rt # R[rd]=R[rs]+R[rt]

- addi rt,rs,imm # R[rt]=R[rs]+SignExtImm

- 例如addi 21,22,-50 # 21=22+(-50)

- 逻辑运算

- and rd,rs,rt # R[rd]=R[rs]&R[rt]

- andi rt,rs,imm # R[rt]=R[rs]&ZeroExtImm

- 例如and 8,9,10 #8=9&10

- 访存 指令

- 分支 指令

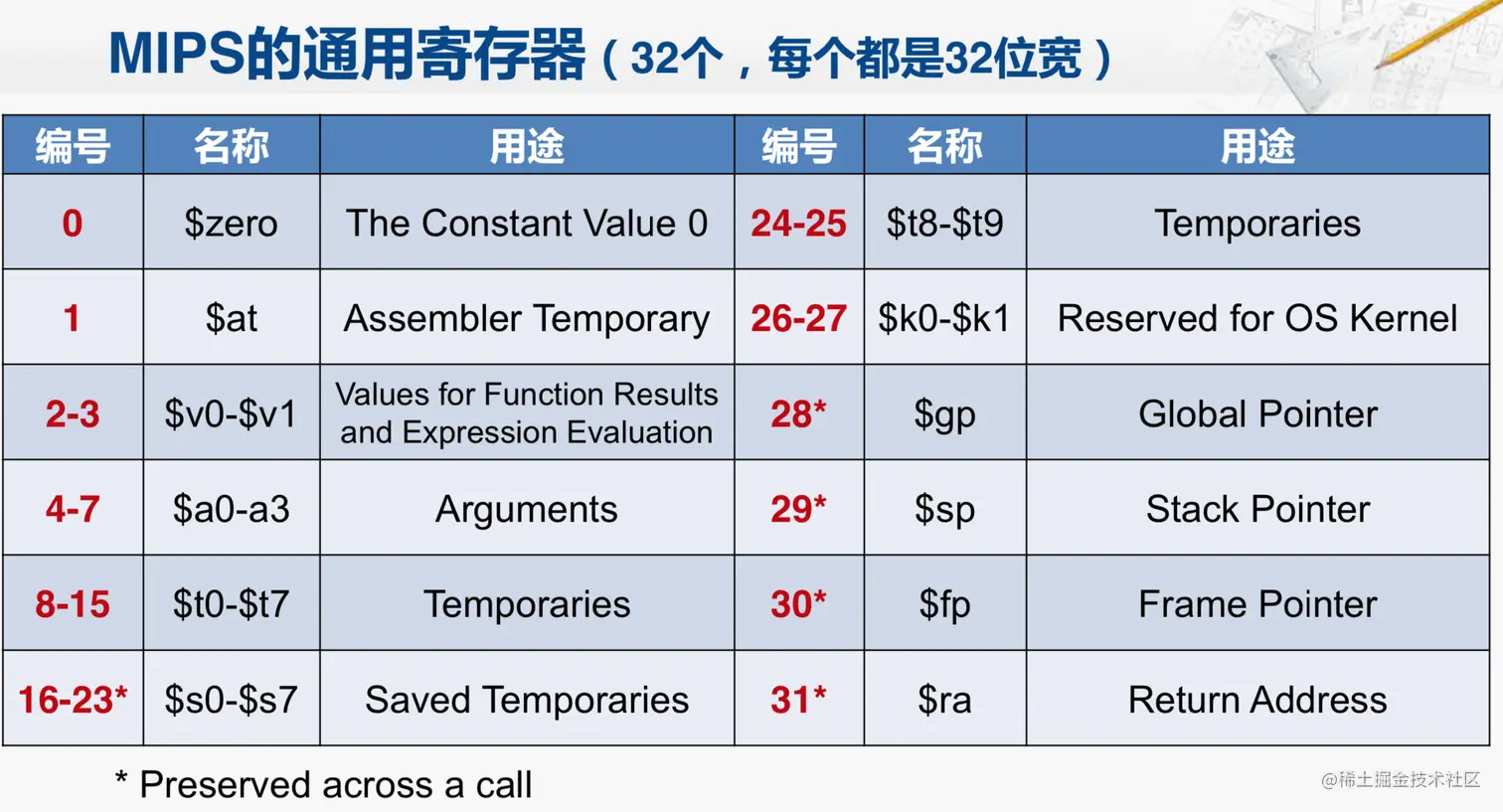

MIPS

- 特点

- 固定的指令长度(32-bit,即1 word)

- 简单的寻址模式

- 指令数量少,指令功能简单(一条指令只完成一个操作)

- 只有Load和Store指令可以访问存储器

- 例如,不支持x86指令的这种操作:ADD AX,[3000H]

- 需要优秀的编译器支持

- 寄存器模型