对一个程序员来说要理解redis、nginx等各种原理,计算机底层机制八成是个迈不过去的砍,不从这里开始研究,各种文章读完后始终觉得缺点啥,整理了一些资料,结合自己的一些理解,记录一个大概出来,如果有哪里不完善,以后再更新。

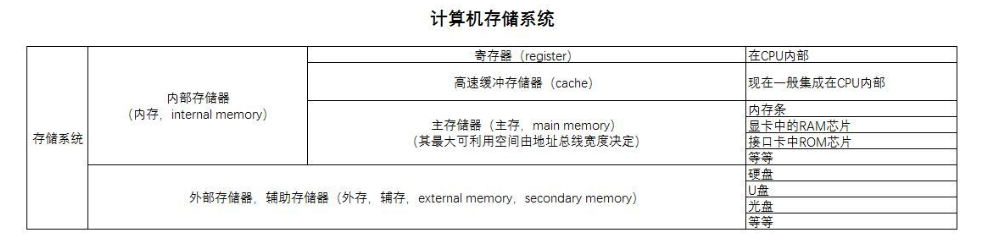

计算机存储系统结构

CPU读取数据流程

CPU->高速缓冲存储器->主存->辅存

分别分析

CPU

CPU组成:

运算器

- 算术逻辑单元(ALU),对数据的逻辑处理,计算

- 累计寄存器(AC)通常叫做累计器,是一个通用寄存器,当ALU处理完算术运算或者逻辑运算之后,会得到一个结果,这个结果就会保存在AC中

- 数据缓冲寄存器(DR)存放从内存中读取的数据

- 状态条件寄存器(PSW)保存的主要是由算术指令和逻辑指令运行或者测试的结果建立的各种条件码内容,一般分为状态标志和控制标志

控制器:控制整个CPU的工作

- 指令寄存器(IR)保存指令,也就是说CPU要执行一条指令的话,需要先把指令从内存上读取,然后放到我们上面说的数据缓冲寄存器中,之后再从DR放到IR中,会有一个叫做指令译码器的东西根据IR的内容生成很多的微操作指令,从而去控制其他部件已完成相应的功能

- 程序计数器(PC)保存着下一条要执行的指令,当一个程序要执行的时候,会把这个程序的起始地址存到这个PC中,执行后,修改为下一条要执行的指令

- 地址寄存器(AR)保存着CPU访问内存上的那一块内存的内存地址,直到内存的读写操作完成

- 指令译码器(ID)对指令做分析的

程序计数器,累加寄存器,标志寄存器,指令寄存器和栈寄存器只有一个,其他的寄存器一般会有多个。

CPU工作步骤

- 取指令 字面意思很好理解啊,不就是拿到需要的指令嘛,那么指令在哪嘞,必须是在内存啊,也就是需要从内存中取出我们需要的指令,然后干嘛,不就是把指令放到CPU中的寄存器嘛,这个取指令就是这么一个过程。

- 指令译码 这个是不是很快想到我们上面说的指令译码器,这个不就是对上一步拿到的指令做分析嘛,干嘛要分析,我得看看你这个指令到底要干啥啊,不然CPU怎么干活嘞

- 执行指令 这个不就更好理解了,就是开始干活啦,实现相应的功能了

- 访问取数 直观上好像没有那么好理解,其实啊,说的就是,我们根据上面的操作,有可能需要从内存中去拿数据,啥意思嘞,要知道,内存存放的是数据和指令,比如执行a+b的操作,我们得到相加的指令,对于a和b都是操作数,它们也是存放在内存中的,是不是也需要去内存中去拿到它们 看上面那个图,0100对应的指令是不是要去0105对应的地址中去拿数据123,这不就是访问取数嘛。

- 结果写回 这又是啥,经过上面那么些个步骤,做的运算肯定得有结果啊,这结果咋弄,你不得保存在哪啊,通常是保存在CPU内部的寄存器中,一般是标志寄存器,这不是就是结果写回嘛

可以看到CPU大部分组成都是寄存器,甚至可以说CPU就是寄存器的集合体

高速缓冲存储器

主存与CPU之间的缓冲,由于CPU运转速度远大于主存的读写速度,因此在两者之间加一层缓存以作缓冲,省的CPU一直等待而空转。一般与CPU物理上集成在一起。

组成

- Cache存储体(高速存储器)

- 地址转换部件:建立目录表以实现主存地址到缓存地址的转换。(联想存储器)

- 替换部件:在缓存已满时按一定策略进行数据块替换,并修改地址转换部件。

工作原理

- 主存储器的地址划分为行号、列号和组内地址三个字段,因此,主存储器划分为若干行,每行若干组,每组包含几个或几十个字,Cache存储体(高速存储器)与主存储器列数,组大小都相同,只是行数较少

- 联想存储器用于地址联想,有与高速存储器相同行数和列数的存储单元。主存中某一单元组存入高速存储器时,记录主存中对应的行号

- 重点来了,CPU读取主存中数据,硬件对存取地址解码,联想存储器将该列全部行号与主存行号对比,有一致的,说明数据已经在Cache存储体(高速存储器)中,直接命中。不一致(脱靶)则直接读取主存,并将单元组调入Cache存储体对应列空着的存储单元组中,将行号更新入联想存储器对应位置单元。

- 如果脱靶(没有命中),Cache存储体对应列又没有空位置,则淘汰对应列某一组,存放新放入的组,称为替换。替换的规则叫替换算法,常用的替换算法有:最近最少使用算法(LRU,需要记录次数,系统开销大,但命中率高)、先进先出法(FIFO)和随机法(RAND)等。替换逻辑电路就是执行这个功能的。

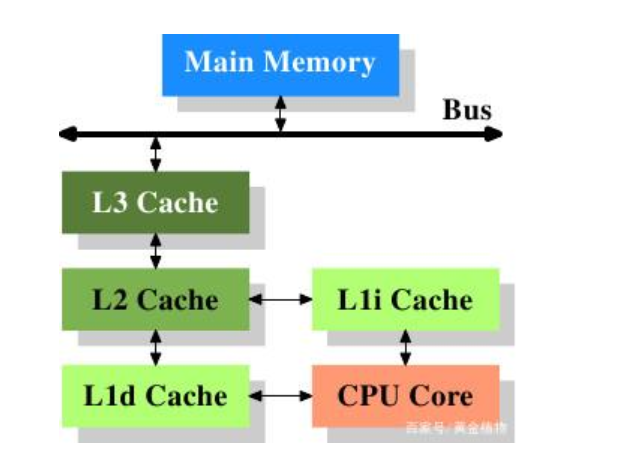

多级结构

L1,L2,L3 三级缓存,CPU优先去L1读取数据,读不到访问L2,再读不到访问L3,再没有再去主存找

容量 L1<L2<L3

速度 L1>L2>L3

作用

- L1的命中率约80%,L2,L3一样,因此真正访问到主存的数据大概只有5%-10%,效率自然大大提升。

- CPU与I/O都要访问内存,I/O的优先级又比CPU要高,现在大部分CPU的访问被高速缓冲存储器搞定了,避免了他俩争抢内存访问,效率进一步提升。

主存

- DRAM :动态随机储存器,其实是SDRAM(同步动态随机储存器),是DRAM的一种

- ROM:只读存储器,出厂时封膜,可读不可写,一般出厂时写入系统程序BIOS

- PROM是可编程ROM,只能进行一次写入操作(与ROM相同),但是可以在出厂后,由用户使用特殊电子设备进行写入。

- EPROM是可擦除的PROM,可以读出,也可以写入。但是在一次写操作之前必须用紫外线照射,以擦除所有信息,然后再用EPROM编程器写入,可以写多次。

- EEPROM是电可擦除PROM,与EPROM相似,可以读出也可写入,而且在写操作之前,不需要把以前内容先擦去,能够直接对寻址的字节或块进行修改。

- 闪速存储器(Flash Memory),其特性介于EPROM与EEPROM之间。闪速存储器也可使用电信号进行快速删除操作,速度远快于EEPROM。但不能进行字节级别的删除操作,其集成度高于EEPROM。

这里要说一下,凭啥CPU读取高速缓冲存储器要比读取主存快呢?

- 高速缓冲存储器(Cache)物理上离CPU更近

- 高速缓冲存储器(Cache)采用SRAM(静态随机存储器),主存采用DRAM(动态随机存储器)。DRAM只含一个晶体管和一个电容器,集成度非常高,可以轻松做出大容量(内存),但是因为靠电容器来储存信息,所以需要不断刷新补充电容器的电荷,充电放电之间的时间差导致了DRAM比SRAM的反应要缓慢得多。

SRAM相比DRAM的复杂度就高了不止一筹。SRAM的特点就是快,有电就有数据,不需要刷新时间所以凸显其数据传输速度很快,缺点就是占据面积大。

辅存

- 内存(主存)直接给CPU提供存储,高速,低容量,价格贵,不能永久保存数据,断电消失,需要从辅存中重新调入数据。

- 外存(辅存)给主存提供数据,低速,大容量,价格低,能永久保存数据。

内存相对来说空间还是太小了,经常在程序运行的时候地址根本不够用,所以还需要借助磁盘等设备来存数据。根据程序执行的互斥性和局部性两个特点,我们允许作业装入的时候只装入一部分,另一部分放在磁盘上,当需要的时候再装入到主存。

这时候就需要苦逼的程序员自己编排好,运行时哪些数据先放到内存里,在运行到一定阶段再删掉内存里的数据,加载另一部分进去。这时候就体现出操作系统的便利之处,借助一些“辅助硬件”,帮助程序员管理调度主辅内存,程序员不用再操心这个了。

从整体看,主辅内存的速度接近于主存的速度,其容量则接近于辅存的容量。