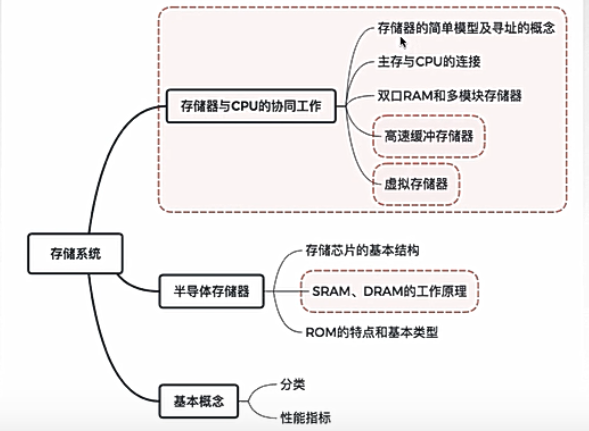

本章总览

(5.1) 存储系统单组成

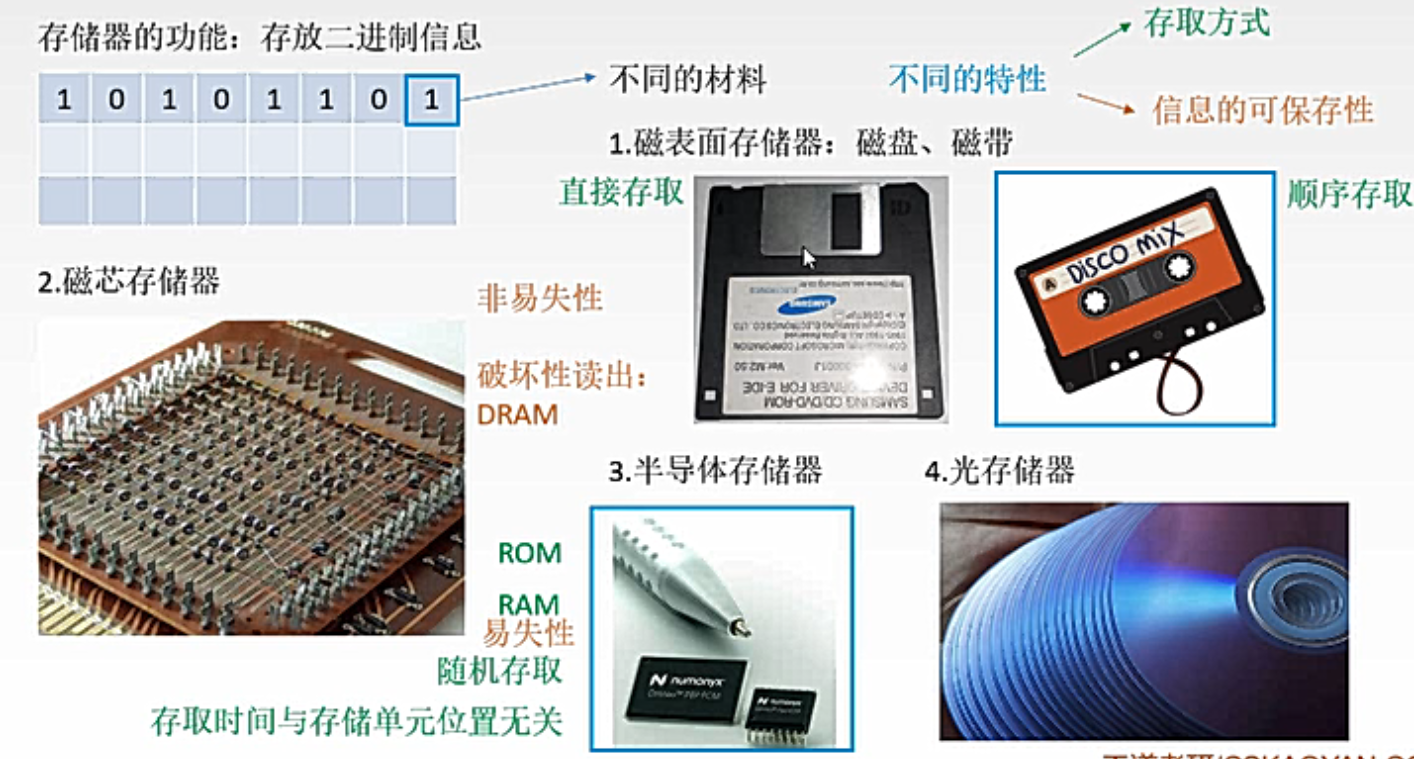

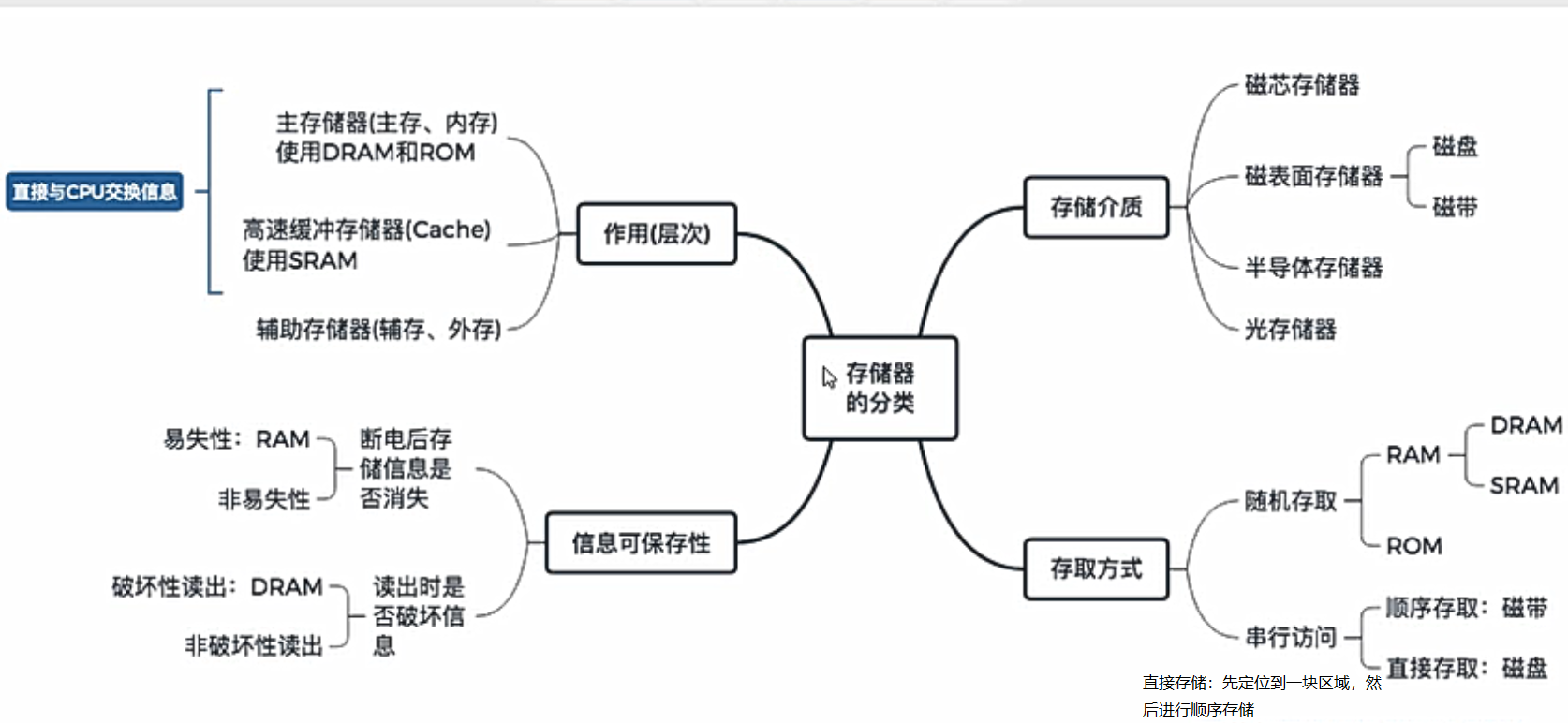

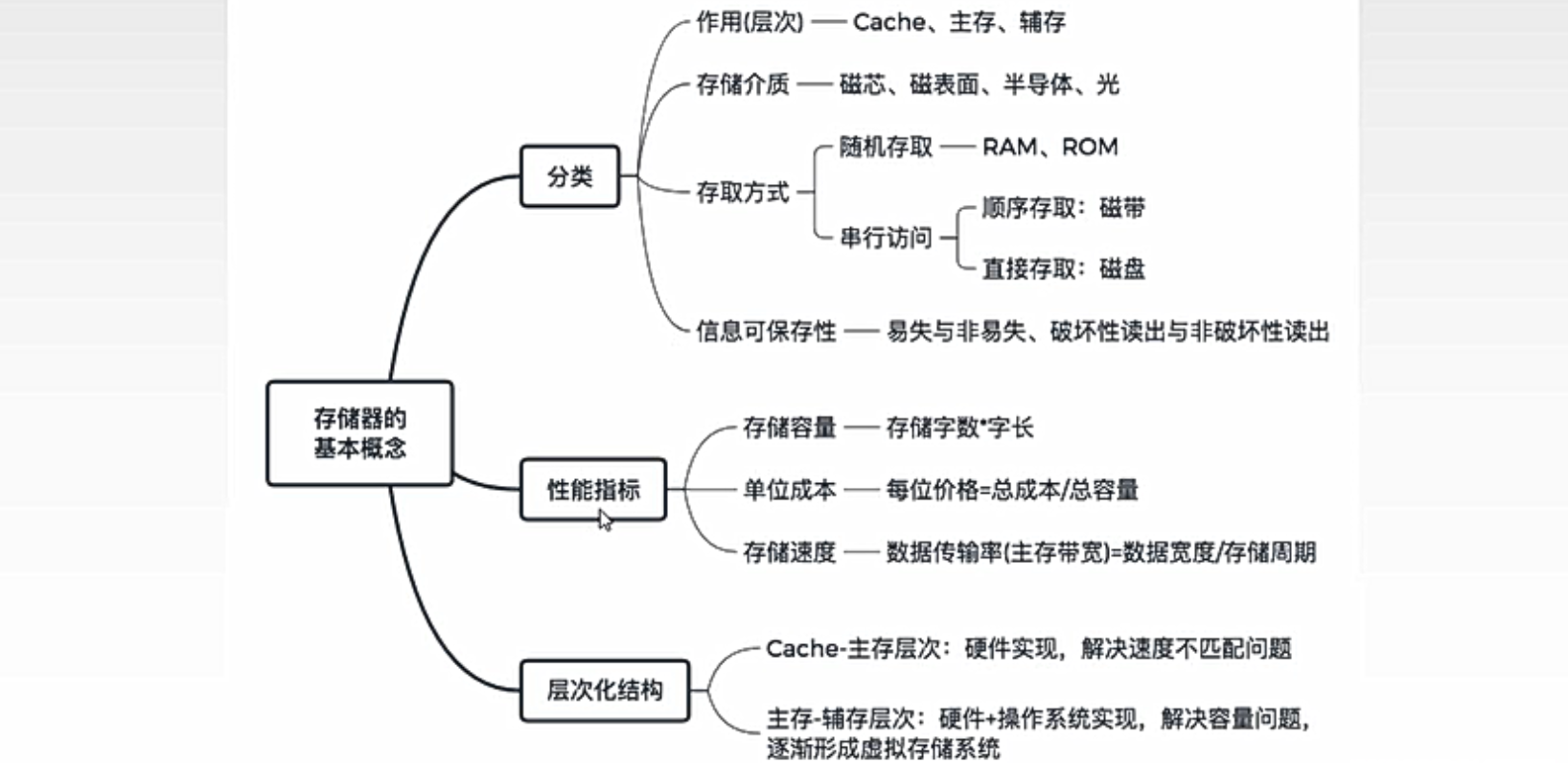

(5.1.1) 存储器分类

1. 按作用分类

2. 按存储方式分类

3. 按存储介质分类

4. 按信息的保存性分类

- 断电丢失信息: 易失性存储器;如,半导体RAM

- 断电不丢失信息:非易失性存储器;如,ROM、磁芯存储器、光存储器。

- 某个存储信息被读出时,原存信息被破坏:破坏性读出。

- 反之:非破坏性读出。

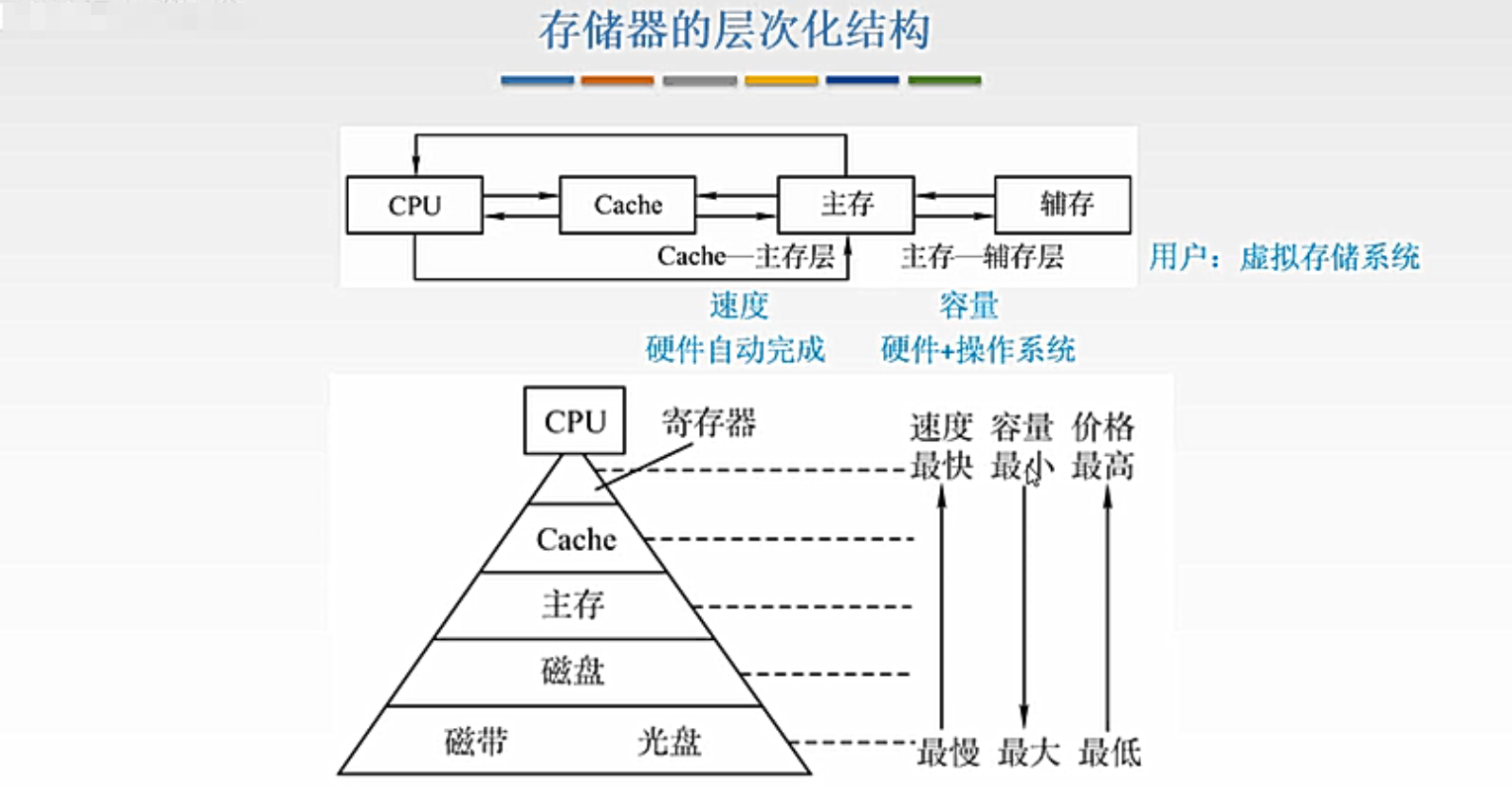

(5.1.2) 存储系统层次结构

(5.2) 主存储器的组织

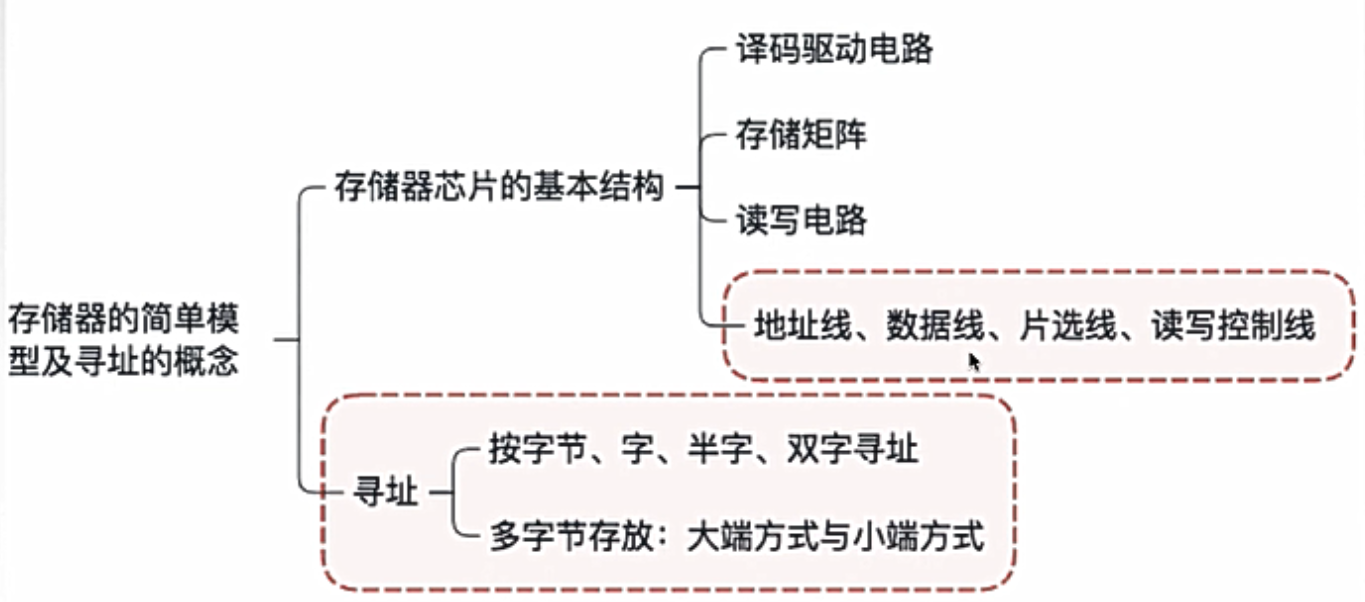

(5.2.1) 主存储器的基本结构

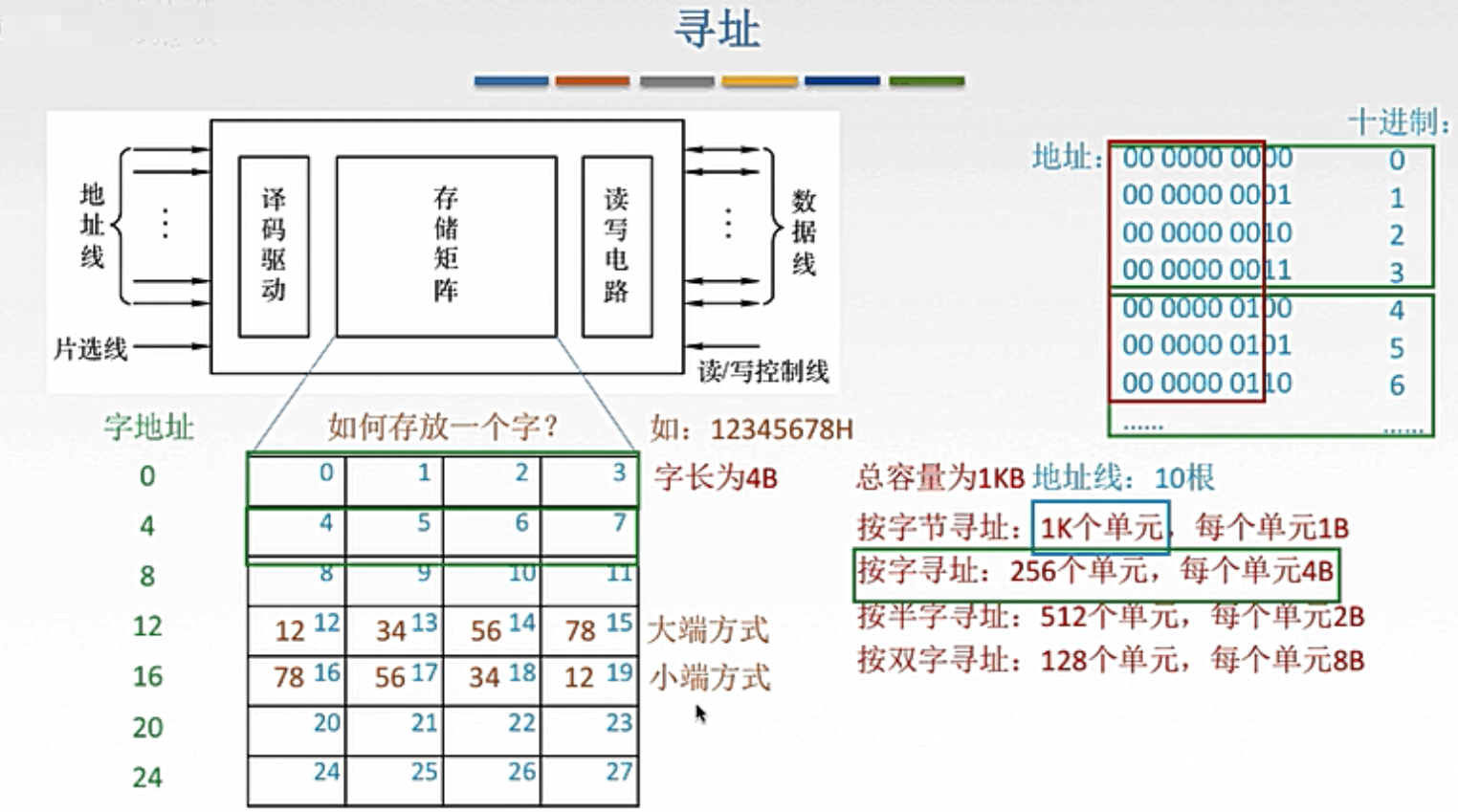

1. 寻址

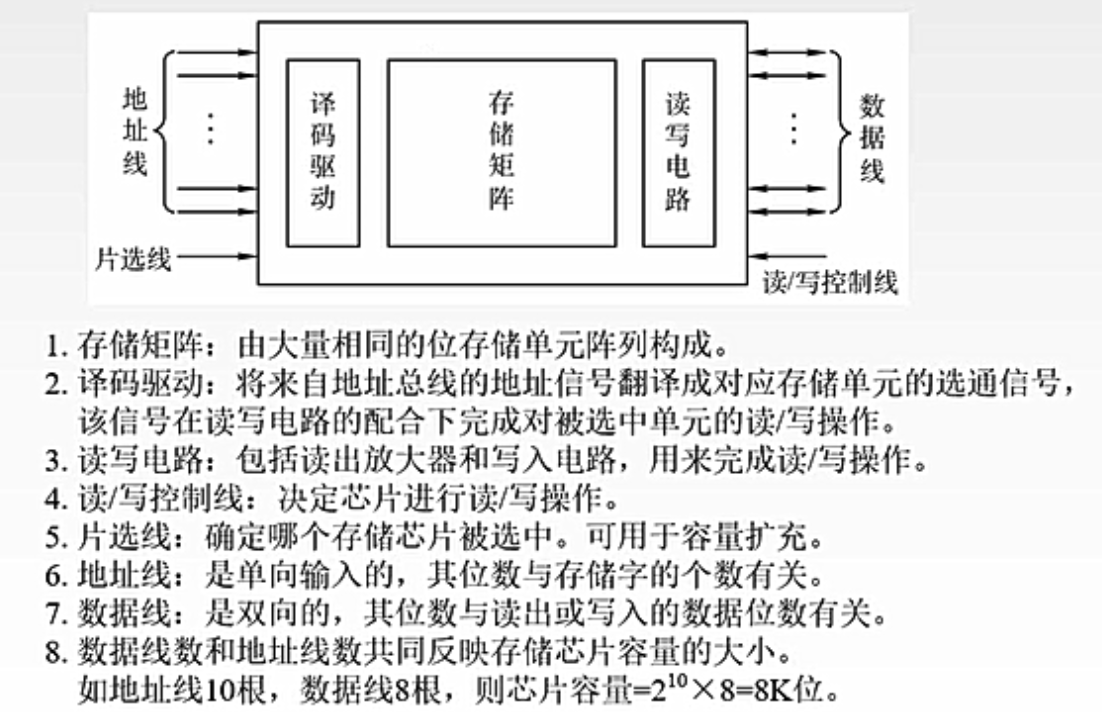

2. 存储器芯片的基本结构

- 译码器:将地址总线输入的地址码换成与之对应的译码输出线上的有效电平,表示选中了某一存储单元。

- 驱动器:提供驱动电流去驱动响应的读写电流,完成对被选中存储单元的操作。

主存的读写操作时在控制器的控制下进行的。

本节总结

(5.2.2) 主存储器的存储单元

位 < 二进制数 < 存储字 < 存储单元(主存单元) < 存储体

- 存储单元需要被编号才能被区分。

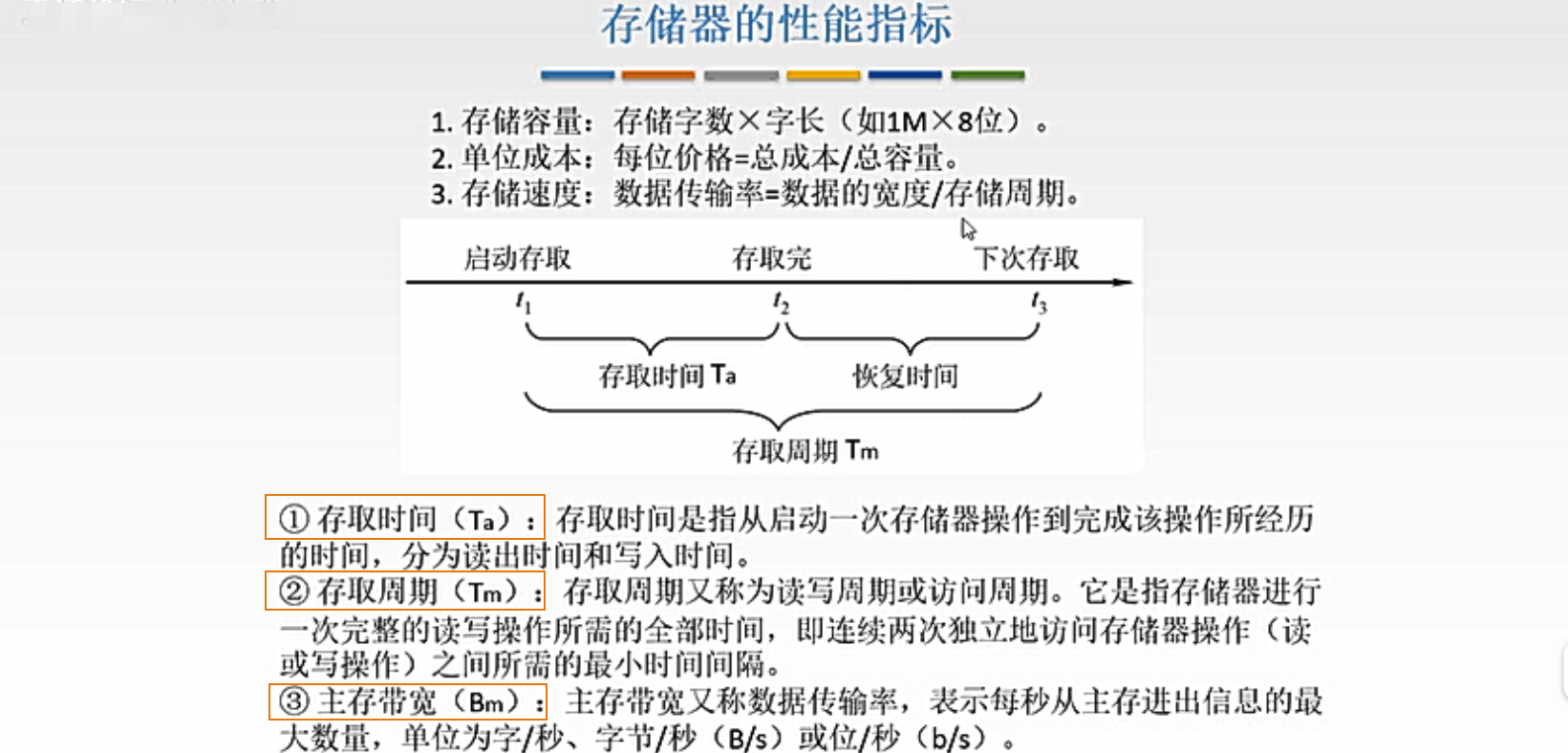

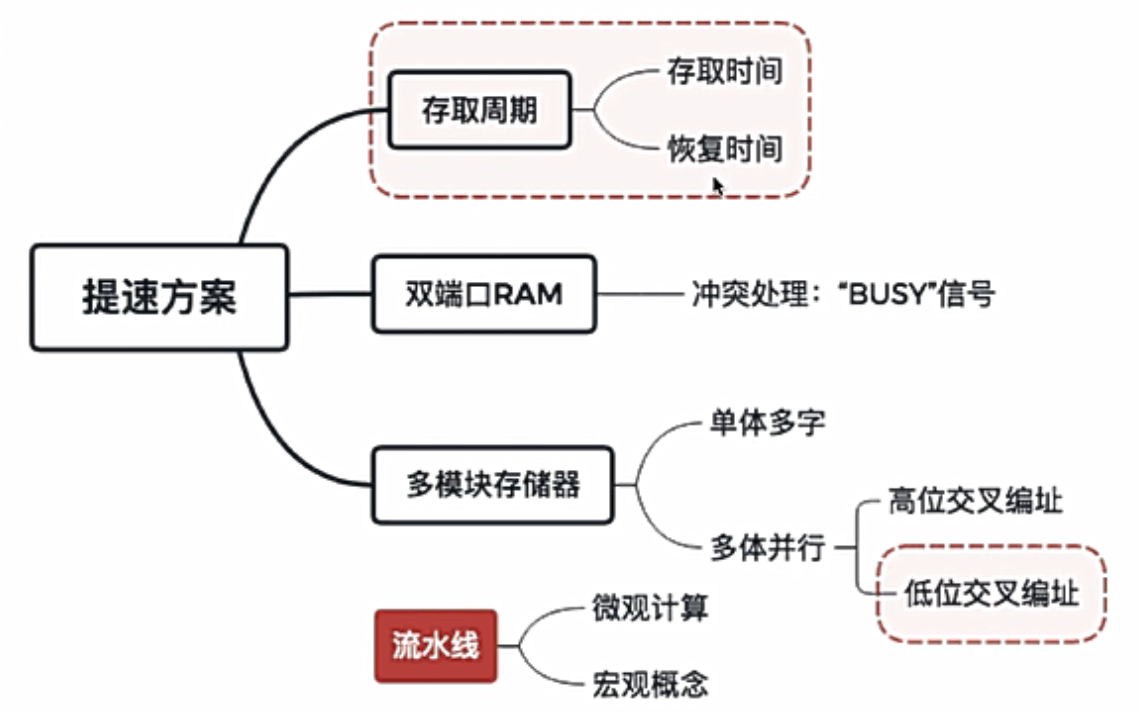

(5.2.3) 主存储器的性能指标

- 主存带宽:也叫数据传输率。表示美妙从主存进出信息的最大数量。

B = 主存等效工作频率 * 主存位宽 / 8- 缩短存储周期

- 增加存储字长

- 增加存储体

- 可靠性:在规定时间内,存储器无故障读写的概率。

- 功耗:耗电能力,以及发热程度。

(5.2.4) 数据在主存中的存放

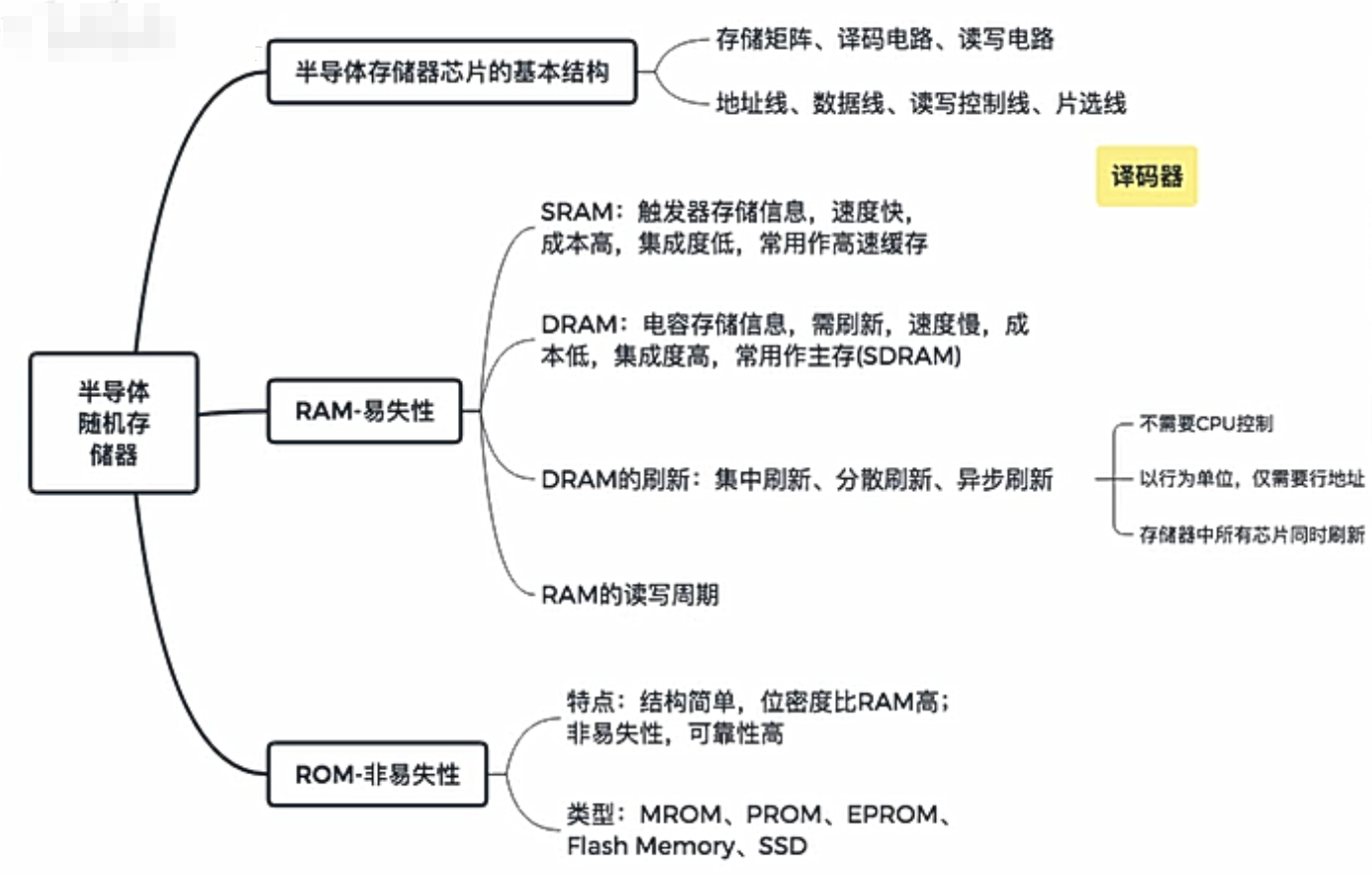

(5.3) 半导体随机存储器和只读存储器

(5.3.1) RAM记忆单元电路

RAM即random-access memory随机存储器。

记忆单元

- 存储器的最基本构件。

- 存放一个二进制位的物理器件。

- 地址码相同的多个记忆单元构成一个存储单元。

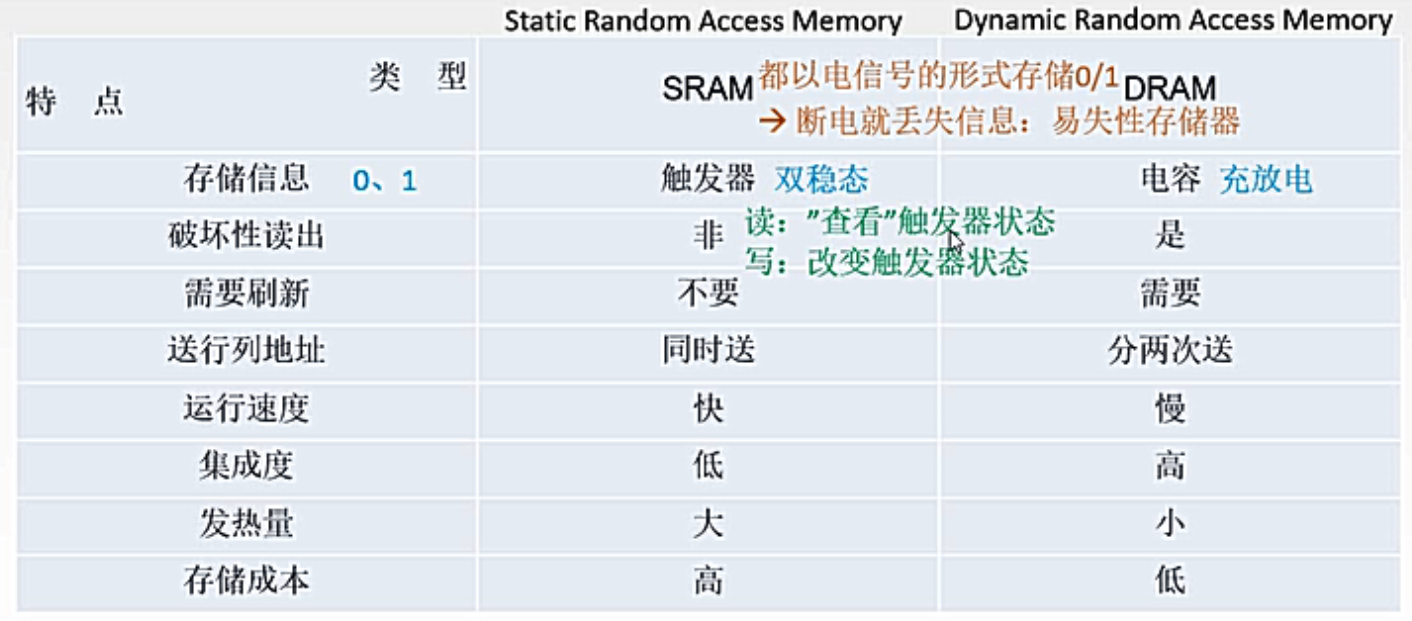

RAM:分为SRAM和DRAM

- SRAM:组成高速缓存。

- DRAM:组成大容量主存。

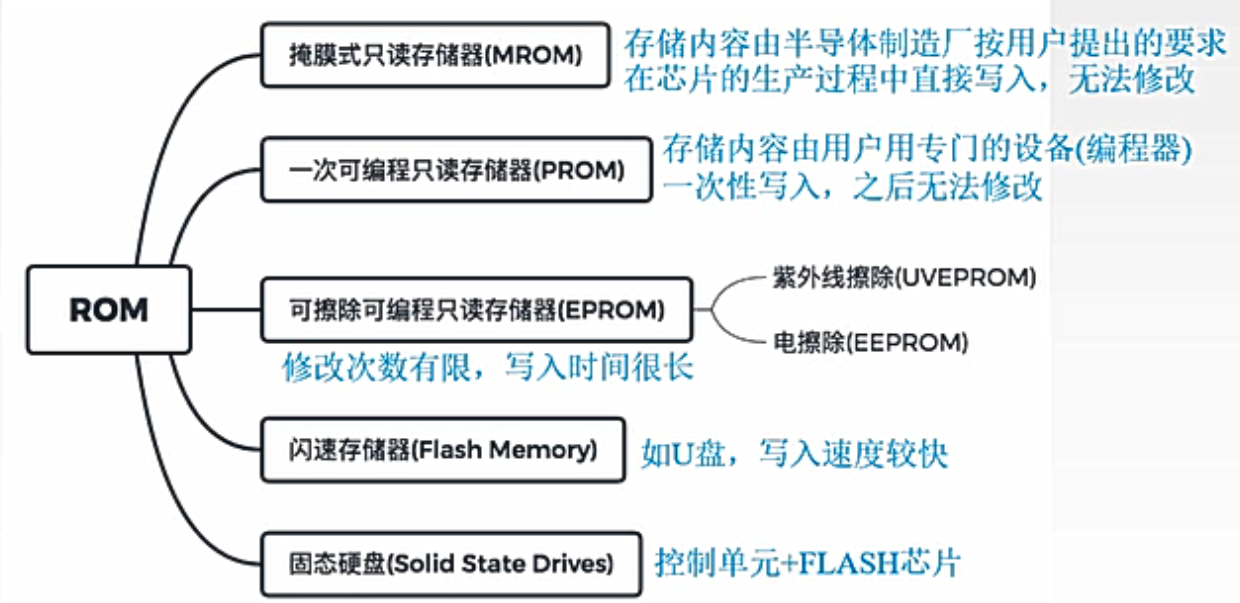

附:ROM

ROM 即 read-only memory,是一种只能读出事先所存数据的固态半导体存储器。

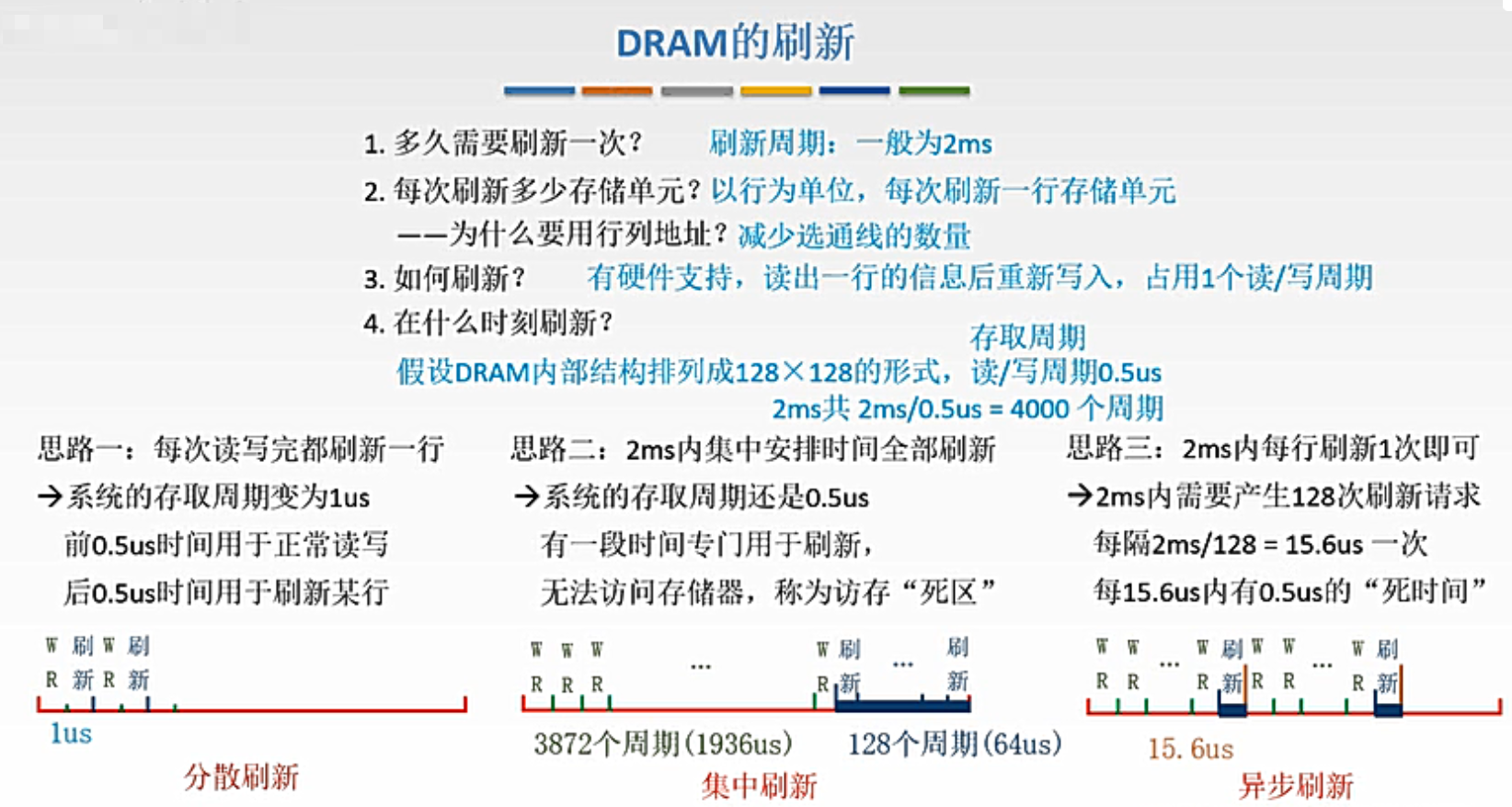

(5.3.2) 动态RAM的刷新

1. 刷新间隔

- 为了维持DRAM记忆单元的存储信息,每隔一定合适的时间

2ms必须刷新。 - 刷新间隔取决于栅极电容上的电荷的泄放速度来决定。

2. 刷新方式

集中刷新

- 刷新时间 = 存储矩阵行数 * 刷新周期

分散刷新

把刷新周期分散到每个存储周期内进行。此时存储周期分为两部分(读写/保持、刷新)

- 如果

32*32为矩阵的芯片的存储周期为0.5微秒,则0.5微秒是刷新时间,则存储周期为1微秒。整个存储芯片刷新一次需要32微秒

异步刷新

- 相邻两行的刷新间隔(刷新周期) = 最大刷新间隔(

2ms)/行数

(5.3.4) 半导体只读存储器

半导体存储器总结

- 易失性:断电之后会失去存储信息。

(5.3.1) RAM记忆单元电路

5.3 总结

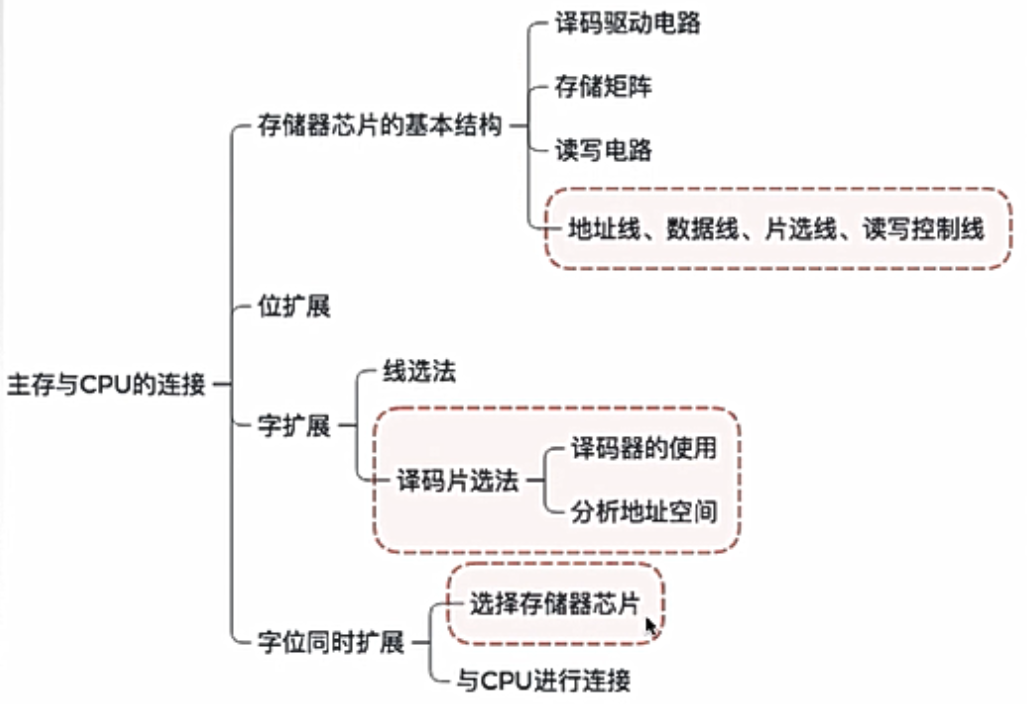

(5.4) 主存储器的连接与控制

主存储器由多个容量有限的存储芯片组成。

(5.4.1) 主存容量的扩展

这一节讨论如何把芯片连接起来的问题。

8K * 1的存储芯片:8*10^10

有10^10次方个存储单元,

有13条地址线(2^13)

有1条数据线

1. 位扩展

在位数方向扩展,而芯片的字数和存储器的字数是一致的。

- 原理是将存储芯片的地址线、片选线和读写先并联起来。

2. 字扩展

在字数扩展,位数不变

- 将地址线、数据线和读写先并联,由片选信号区分各个芯片。

3. 字和位同时扩展

5.4 总结

(5.5) 提高主存读写速度的技术

略...

(5.6) 多体交叉存储技术

(5.7) 高速缓冲存储器

重点内容

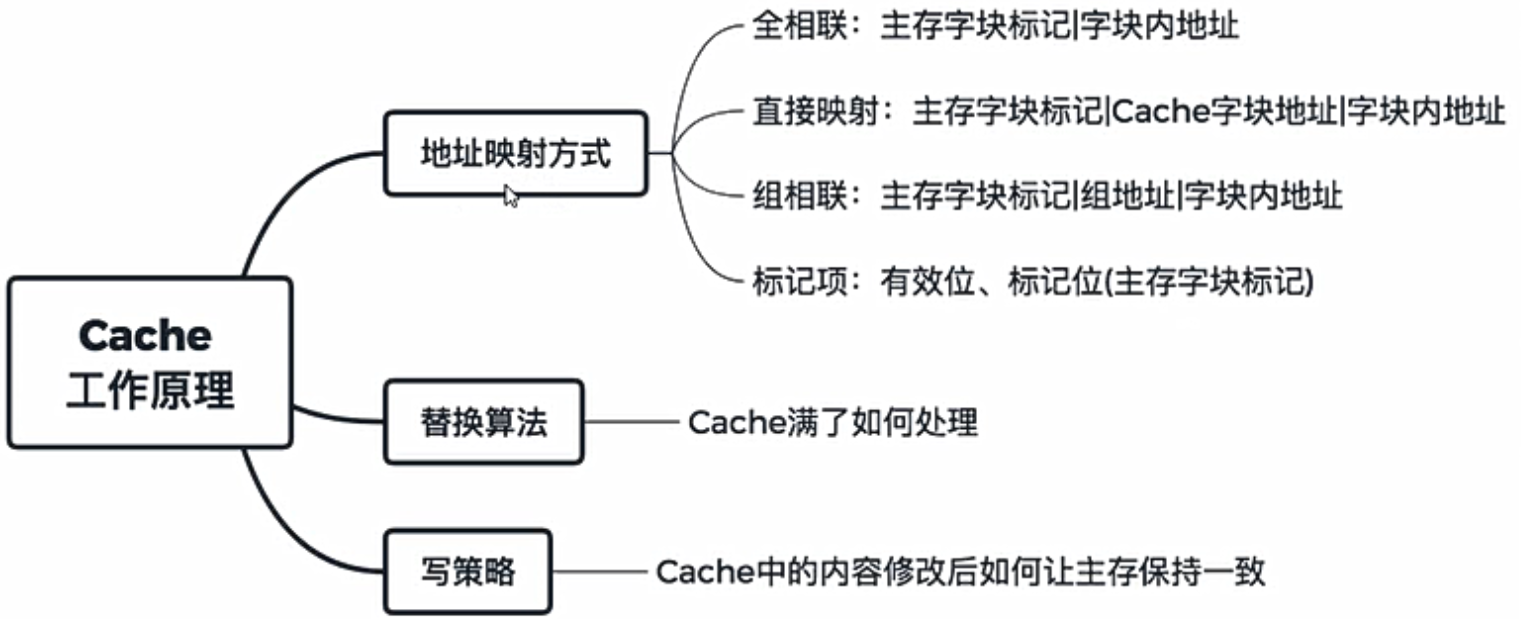

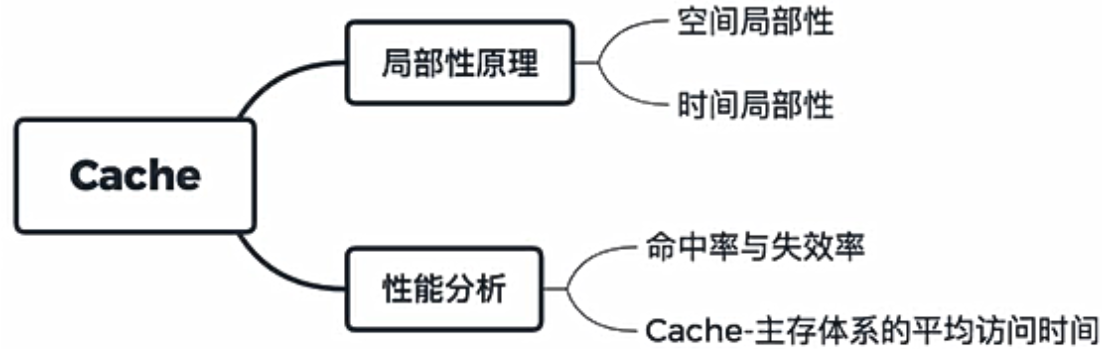

(5.7.1) 高速缓存工作原理

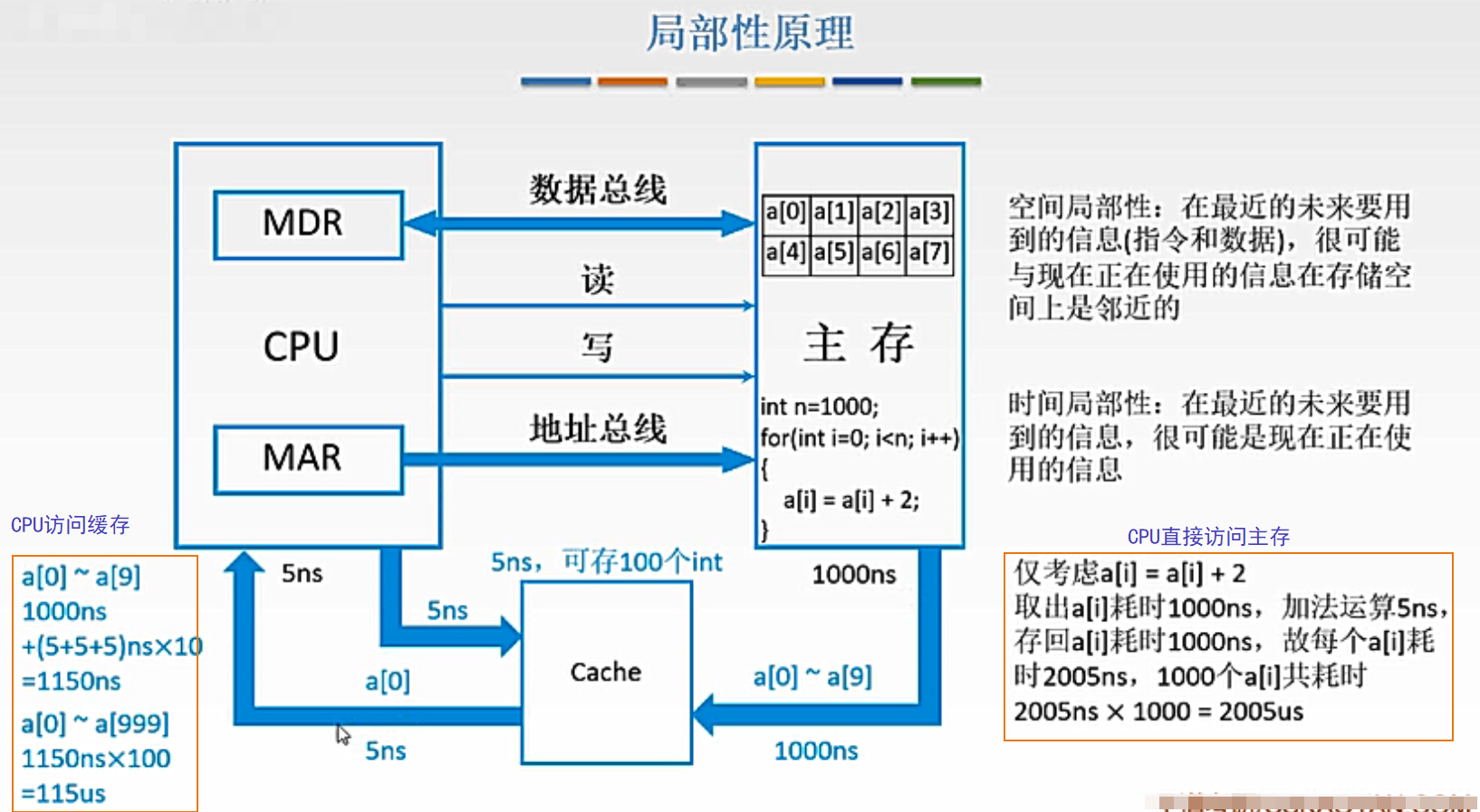

1. 程序的局部性原理

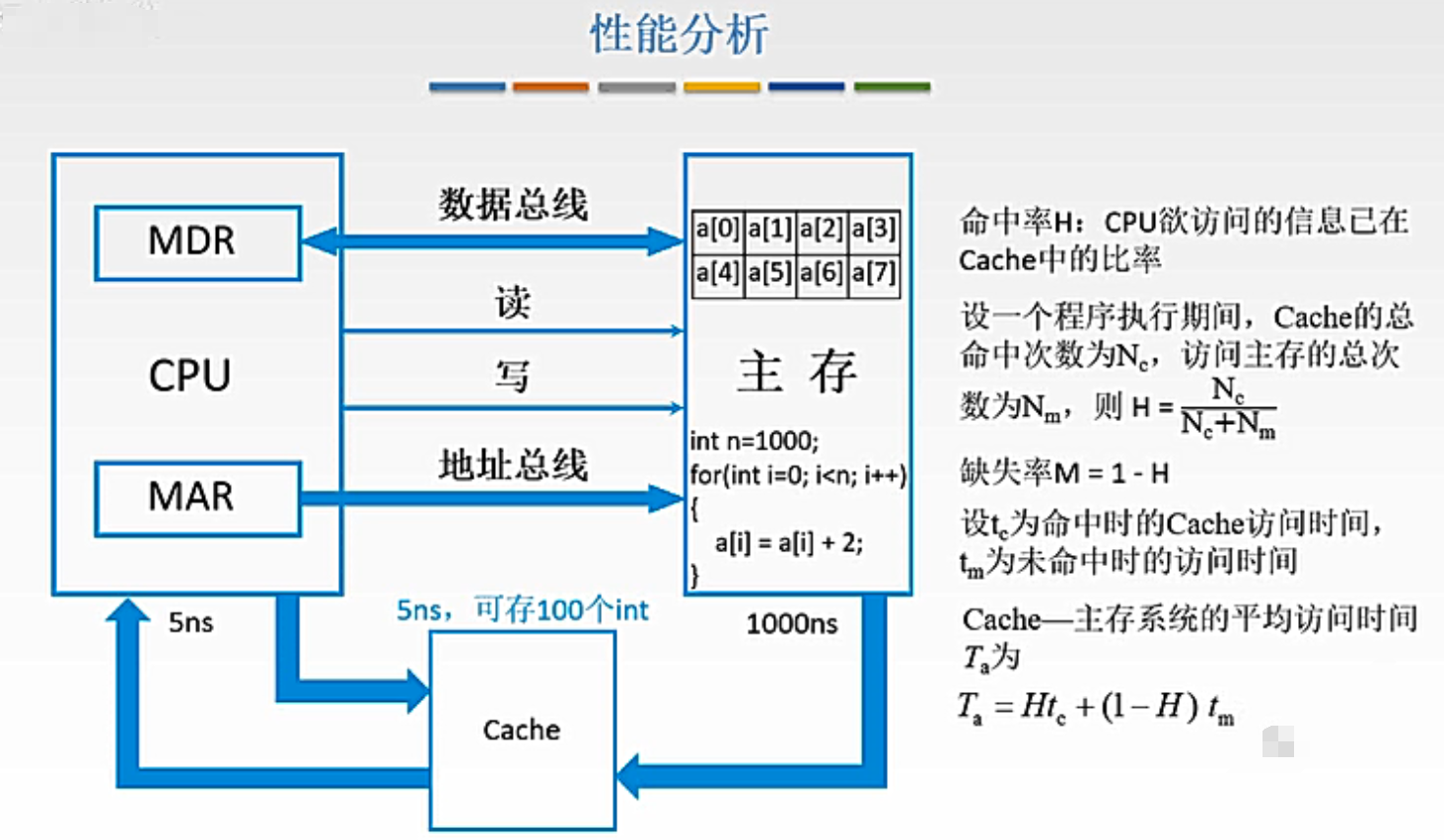

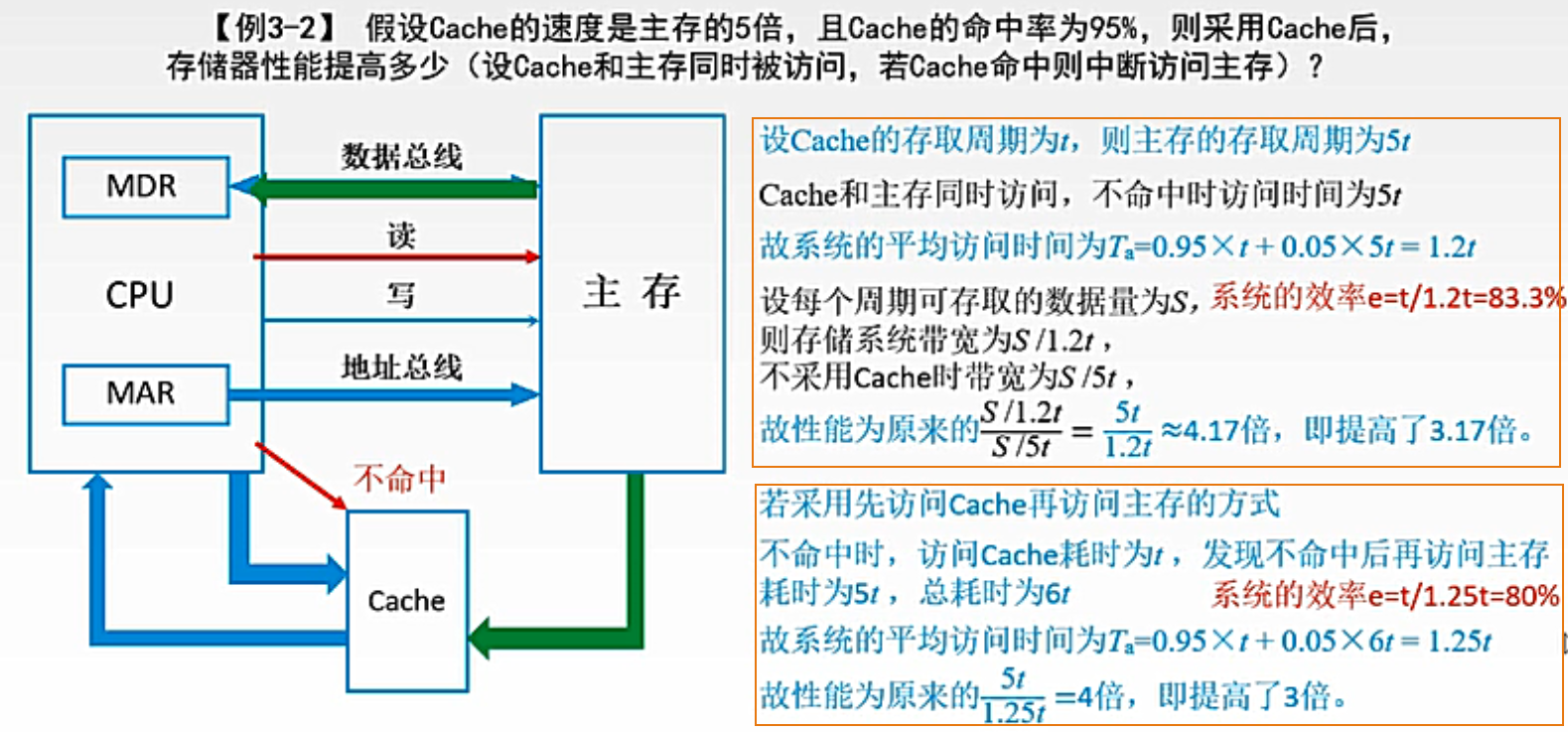

性能分析

例题

本节总结

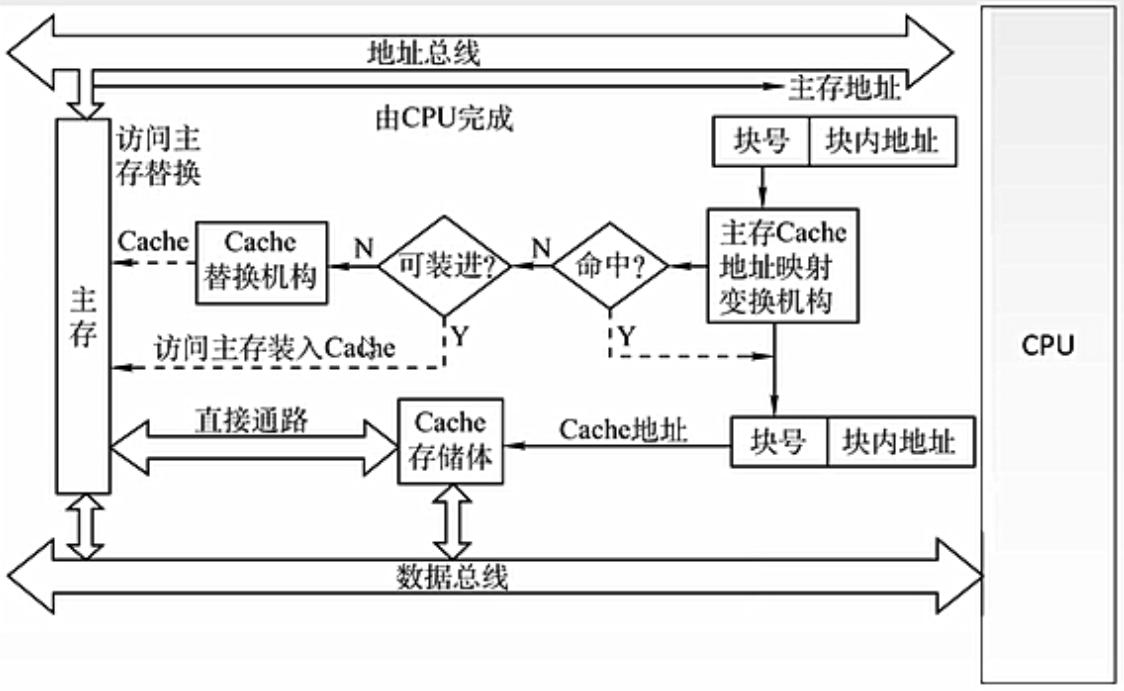

2. Cache的基本结构

(5.7.2) Cache 的读写操作

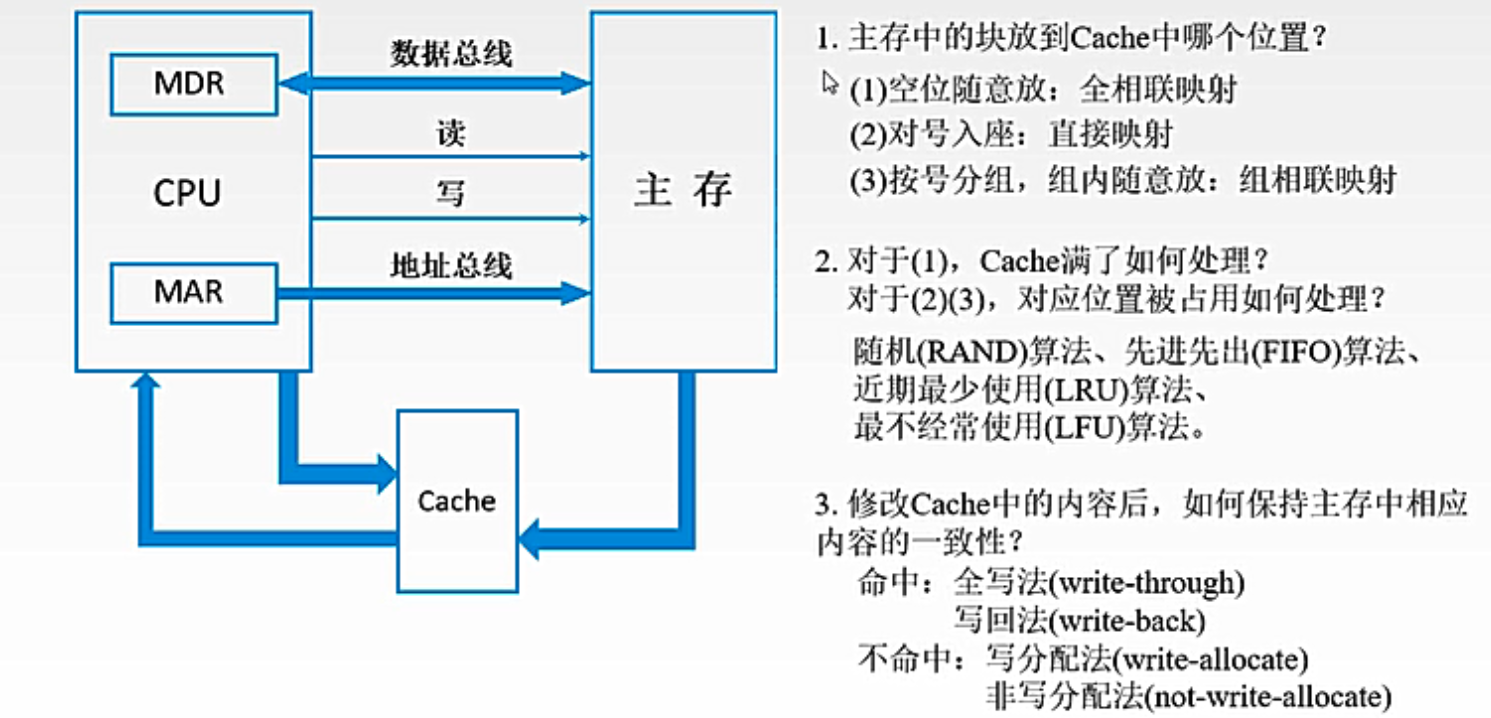

使用缓存要解决的三个问题

1. Cache 的读操作

- 如果缓存命中,直接访问缓存。

- 不命中,访问主存,并将该块信息一次从主存中调入

Cache内。

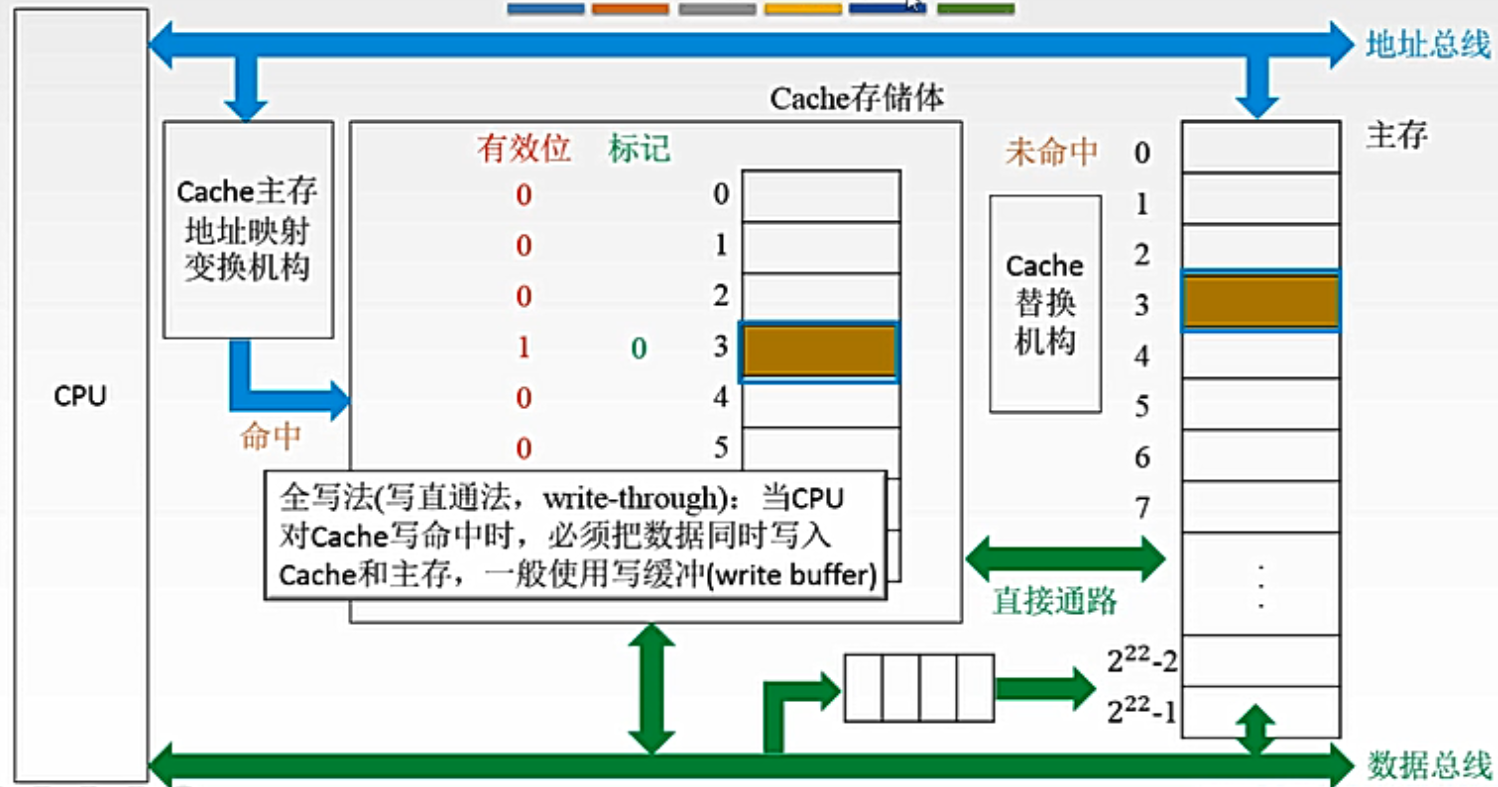

2. Cache的写操作

当CPU发出写请求时,可能会存在Cache的内容与主存内容不一致的问题。

- 当cpu把Cache的某个内容

X改成了X',但主存中的内容仍然是X。- 如果Cache命中需要有处理方法:直达法、写回法(见5.7.5)。

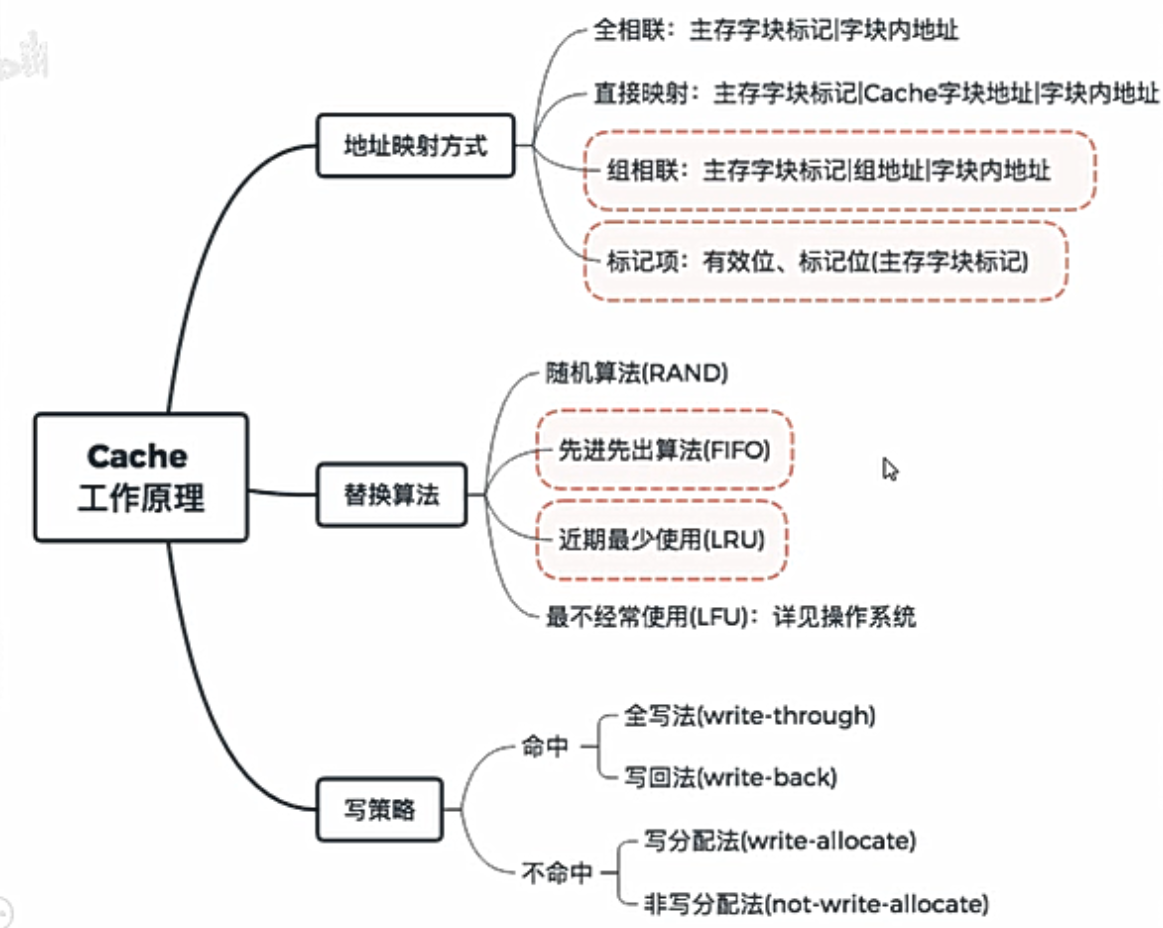

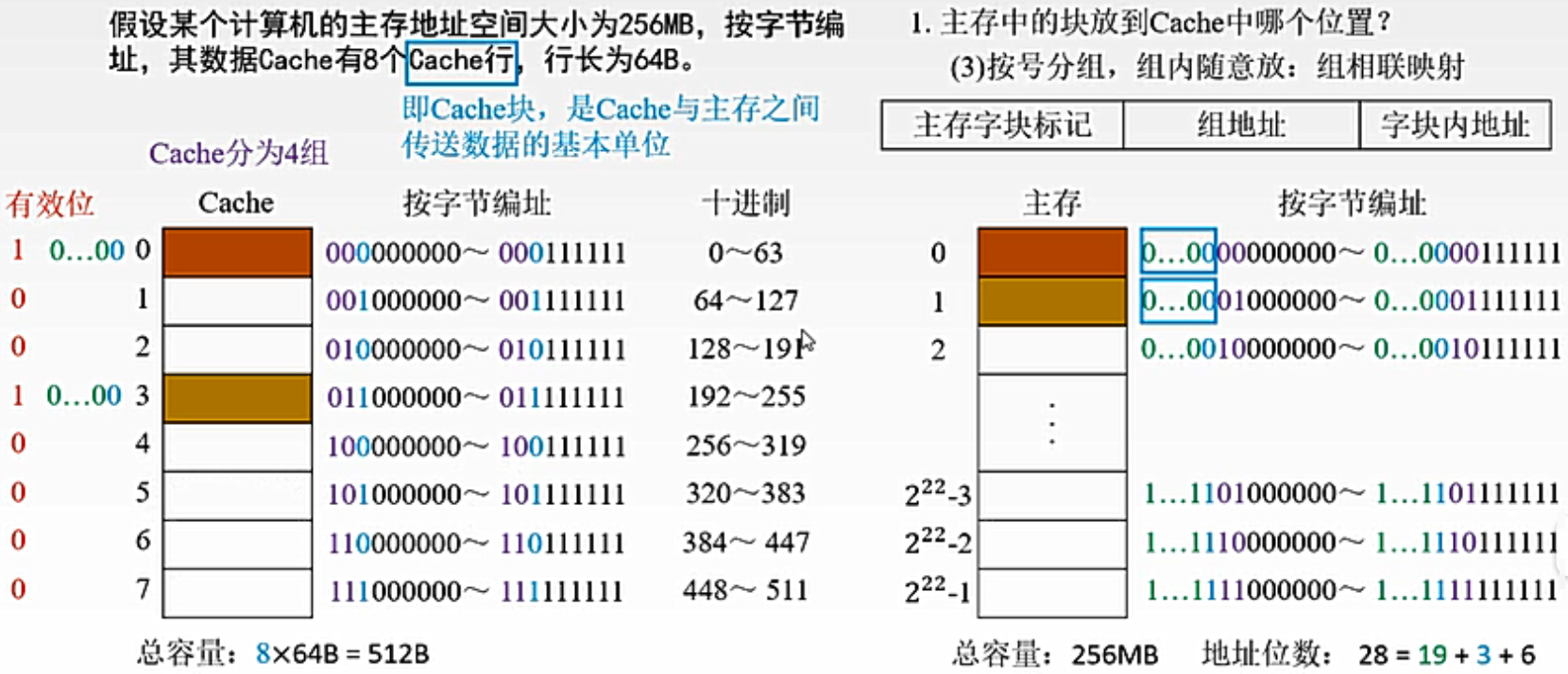

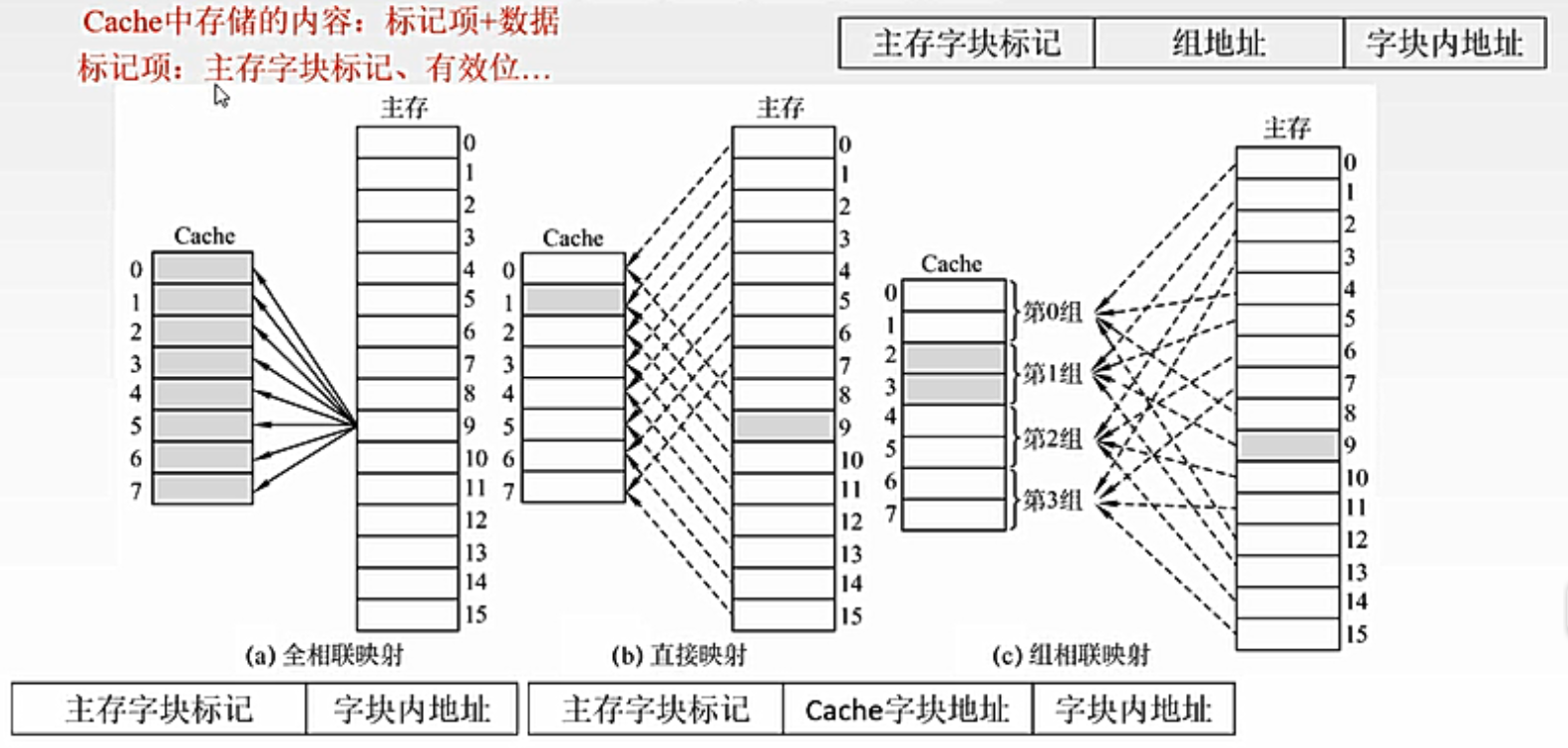

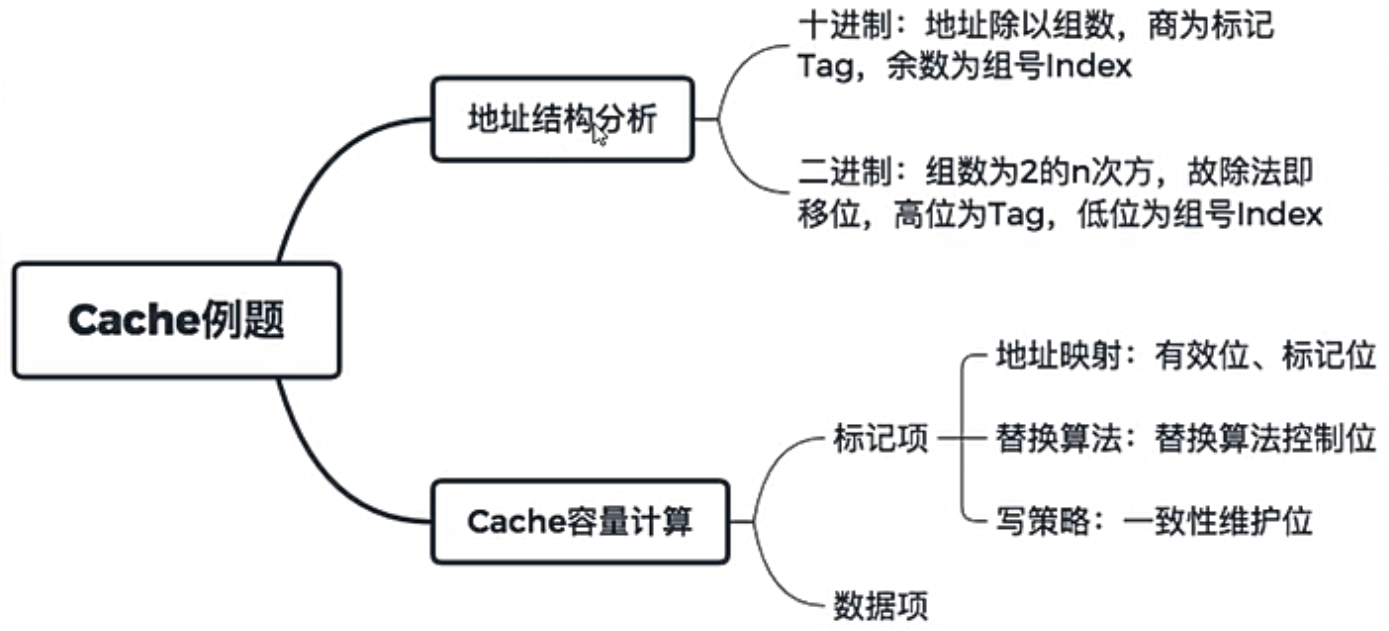

(5.7.3) 地址映射

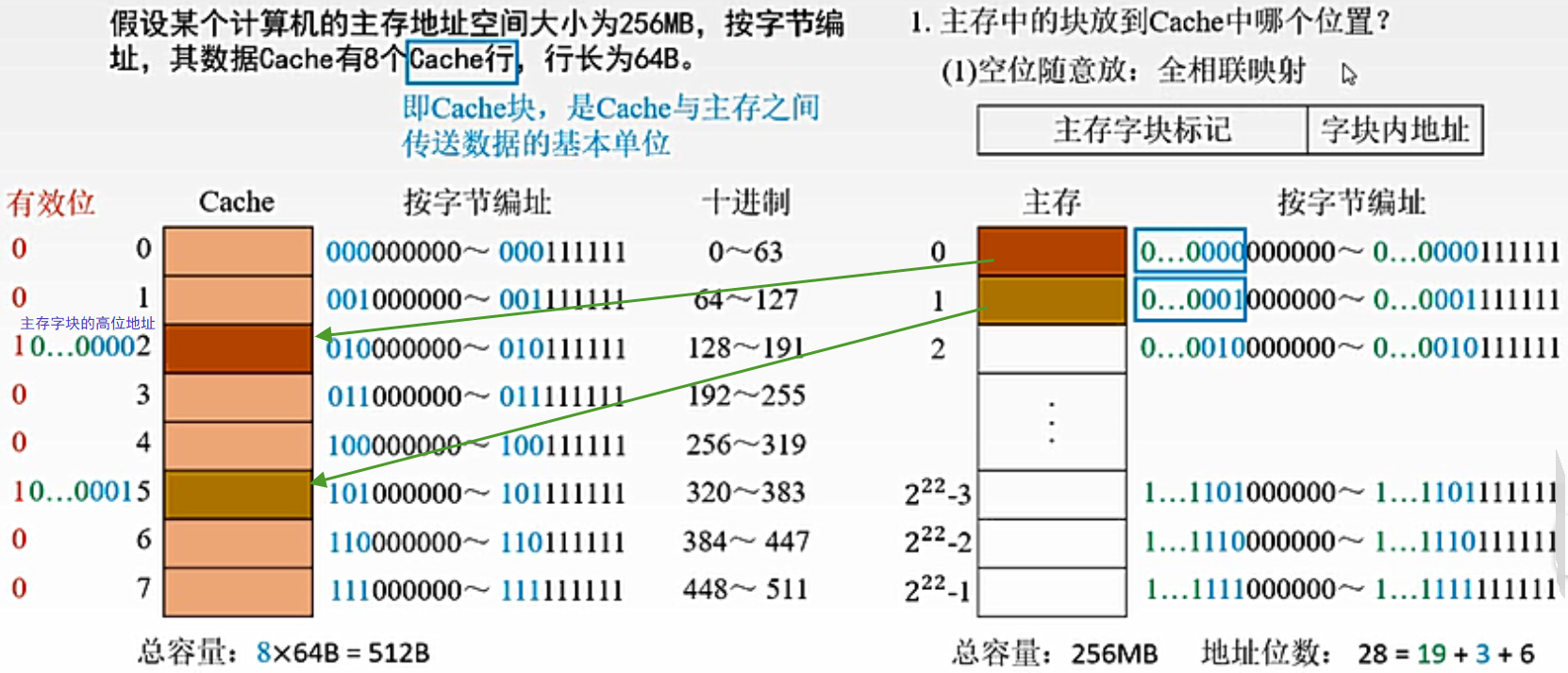

1. 全相联映射

Cache中作为标识。

- 优点:地址冲突概率最低、空间利用率最高。

- 缺点:地址变换速度慢、成本高、实现困难。

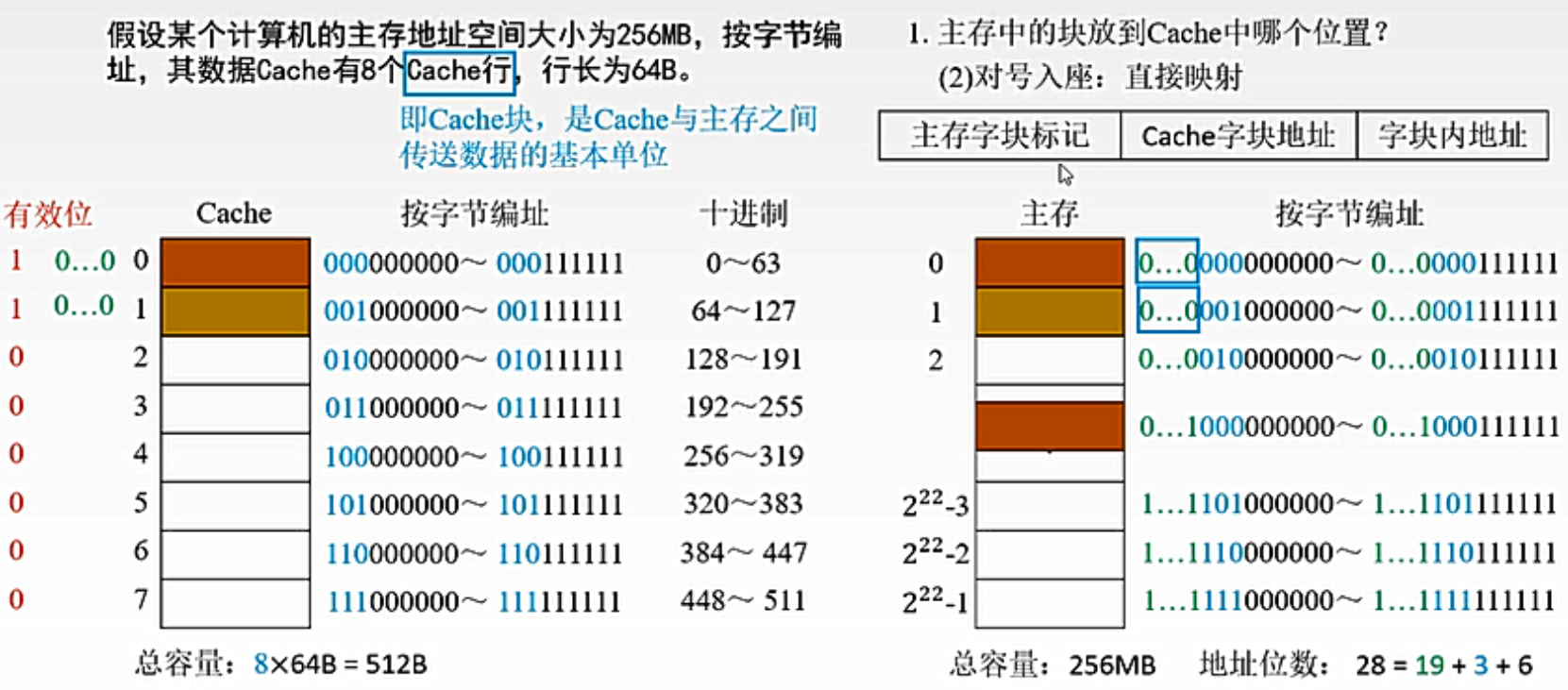

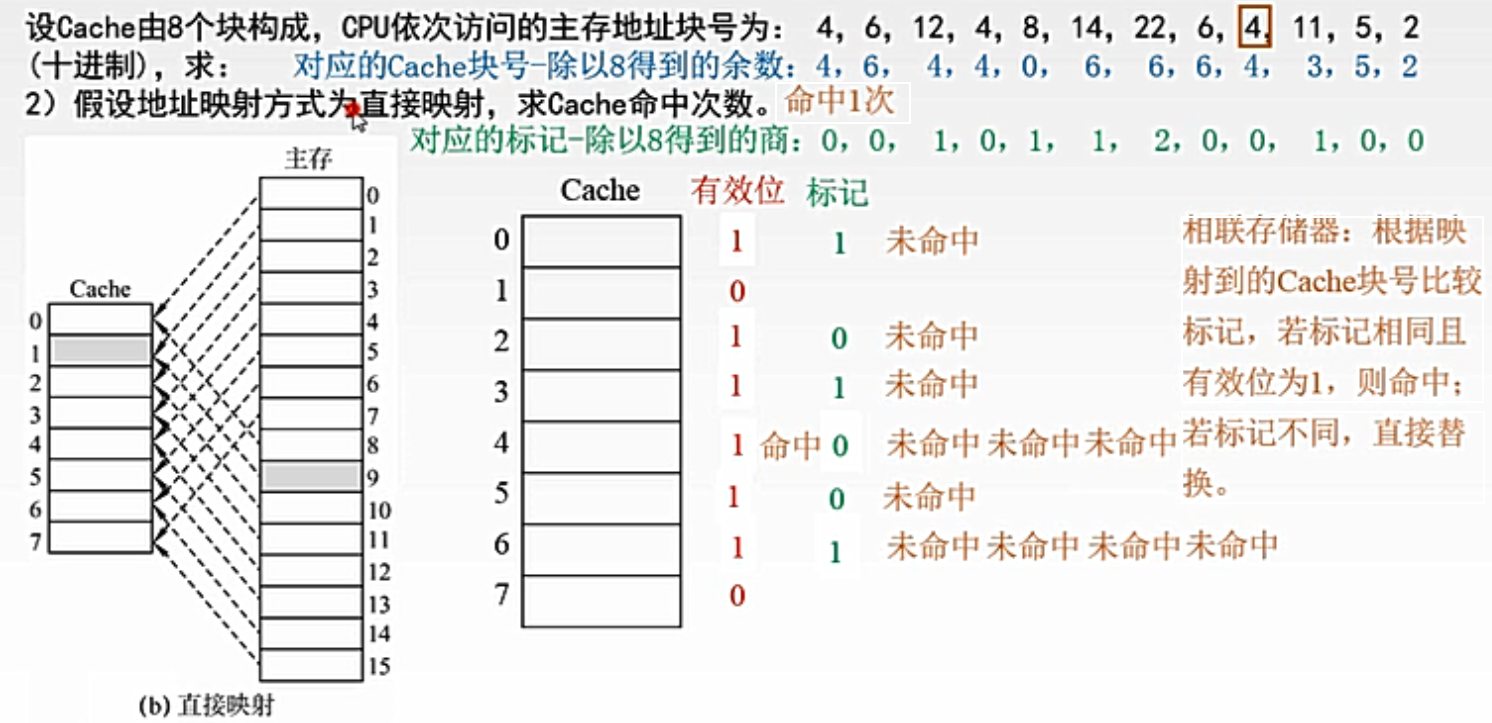

2. 直接映像

- 优点:成本低、易实现、地址变换速度快。

- 缺点:地址冲突概率高、空间利用率低。

- 如果Cache块号冲突,直接移除原内容;

- 拿上图的例子说明,如果主存8号要存进Cache,那只能存进Cache的

0号位置(如果0号有内容),即使0后面有空位,还是不能存入。

Cache位置 K = 主存的快号 % Cache的总块数

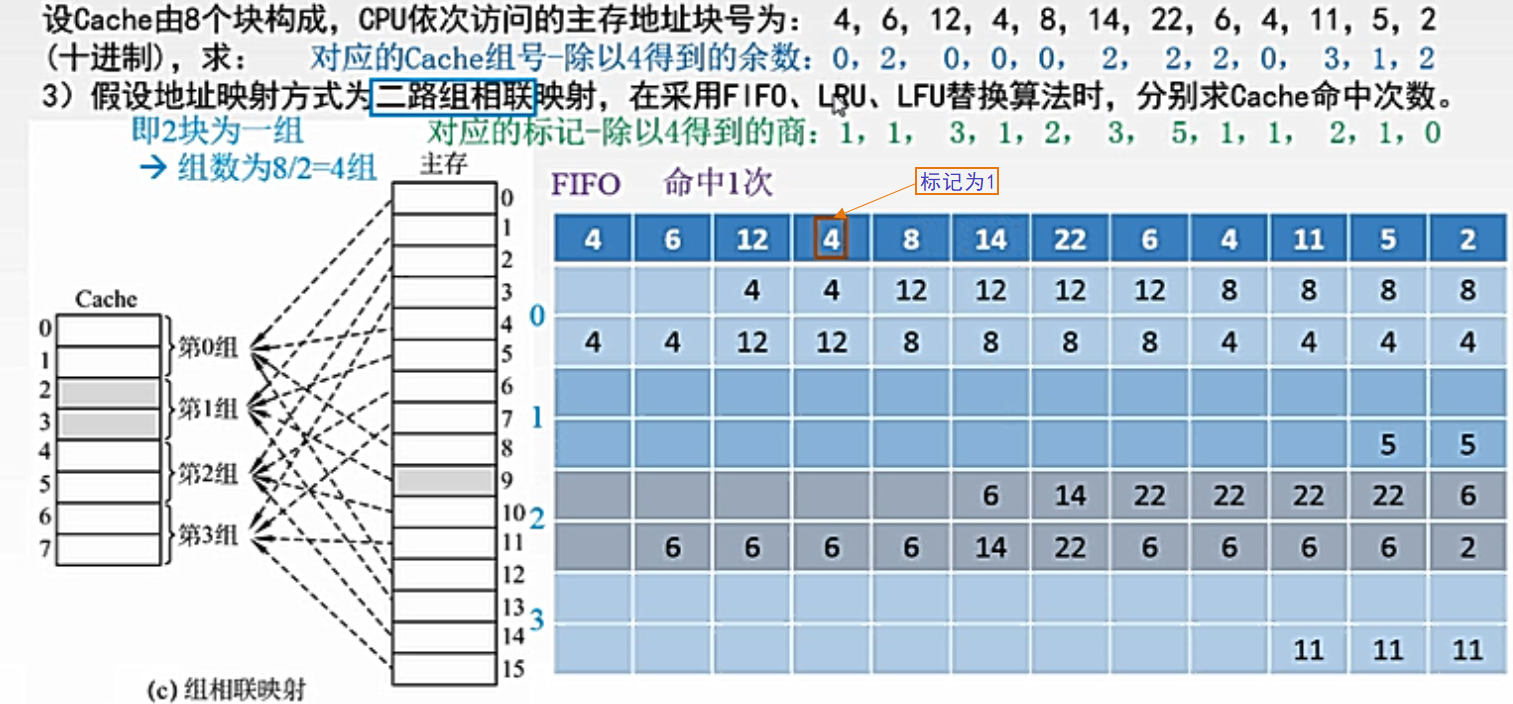

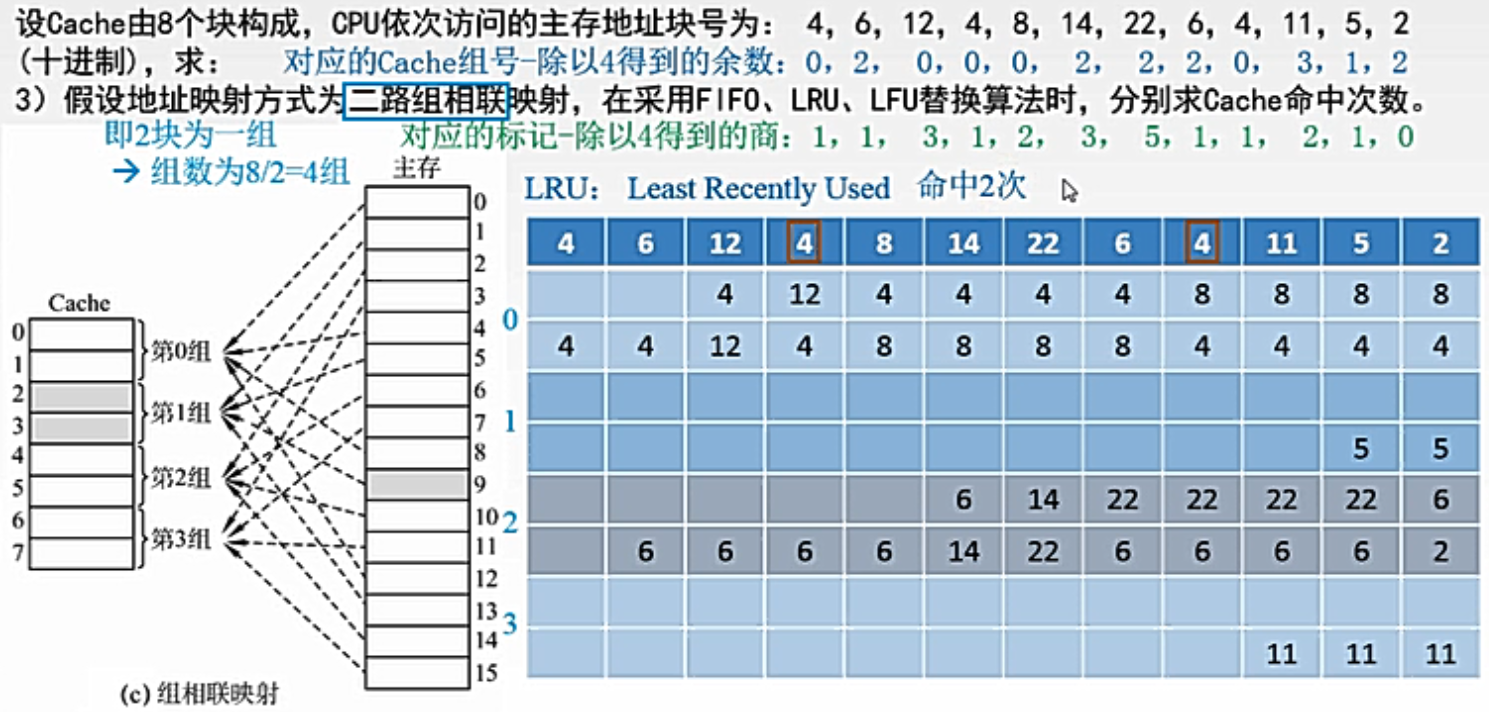

3. 组相联映像

- 在确定组号后,在本组内使用全相联映射的方式。

- 该方法如果组内的块容量为1,直接转换为直接映像;

- 当组内的块容量为Cache的容量是,则转换为全相联映射。

关系计算:Cache的组号 = 主存的块号 % Cache的组数

- 得到的余数就是Cache的块号。

- 得到的商就是标记位。

- 结合余数和商就可以把该内容对应主存的位置复现出来。

4. 三种映像总览

- Cache存储的内容:标记项、数据。

- 标记项 = 主存字块标记 + 有效位。

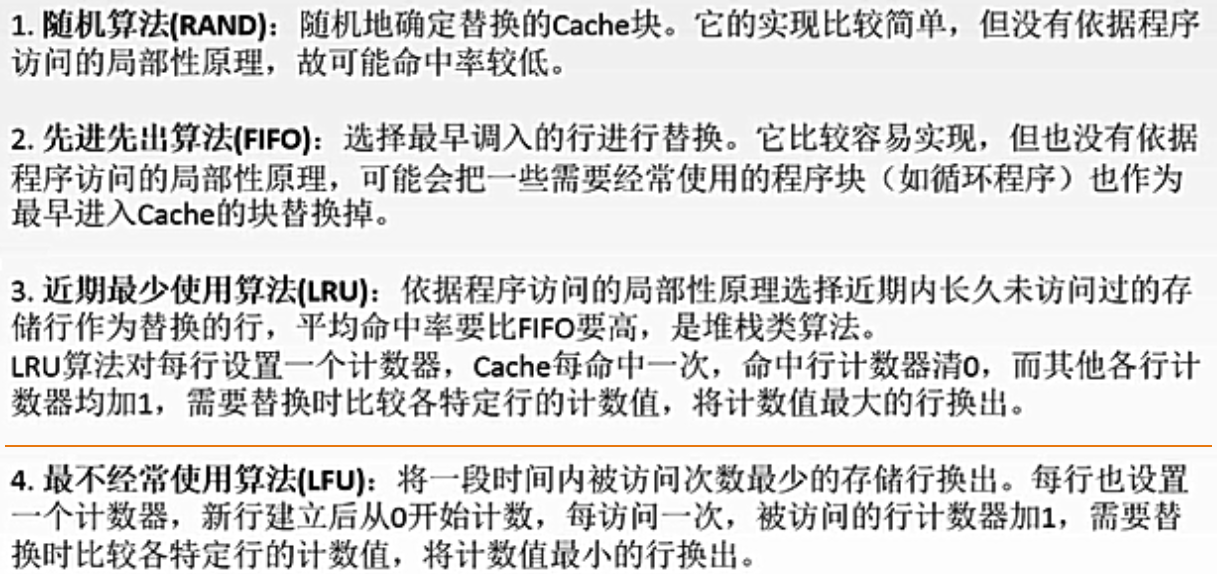

(5.7.4) 替换算法

- 对于第3种算法来说:如果一个块很久之前存进了

Cache,假如在今天被使用了一次,那么他的计数器被置为0,那它在本算法内也被认为是非最少使用。

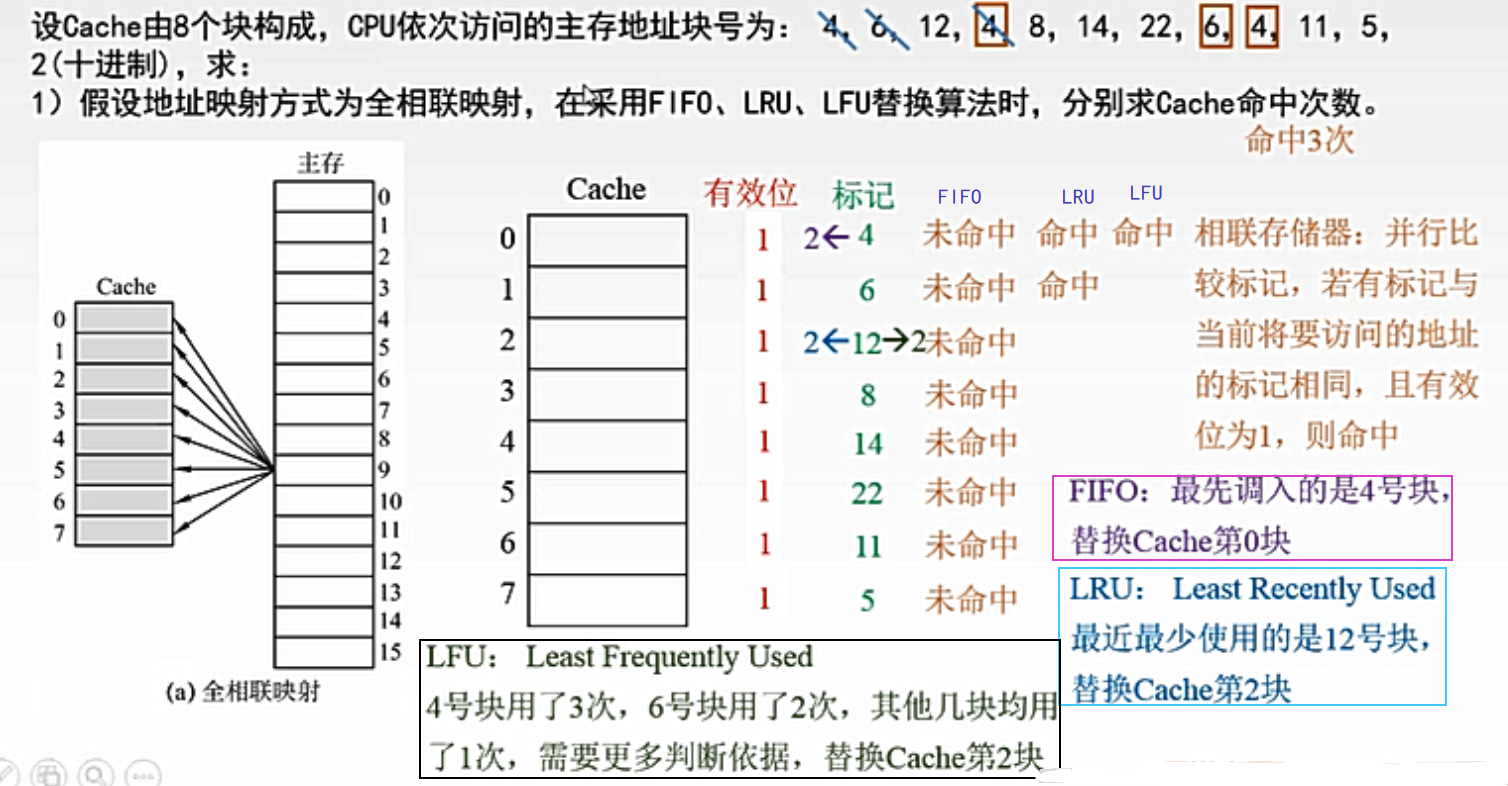

例题

(1)全相联映射

2<-4:表示2进入的时候,缓存满了,需要替换

(2) 直接映射

- 写出主存地址块号对应的

Cache地址块号 = 主存地址块号 % Cache块数(余数) - 写出对应的

标记 = 主存地址块号 / Cache块数(商)

(3) 组相联映射

准备工作

- 画出表头(由主存地址块号组成)

- 写出主存地址块号对应的

Cache地址块号对应的组数 = 主存地址块号 % 组数 - 写出主存地址块号对应的

标记位 = 主存地址块号 / 组数

FIFO策略答案

LRU近期最少使用策略

(5.7.5) 缓存更新策略

缓存命中时

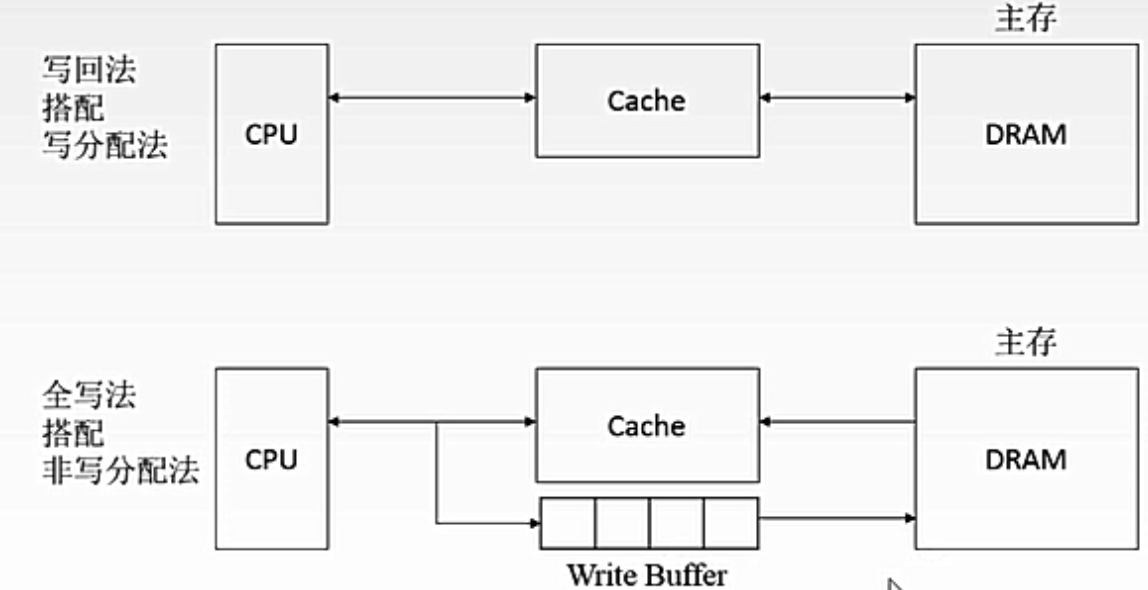

1. 写直达法

- 写直达法:cpu在执行写操作时,必须那数据同时写入Cache和主存。当某一块需要替换时,也不必把这一块写回到主存中,新调入的块直接覆盖旧的。

- 特点:实现简单,而且可保持主存数据的正确性,但可能增加主存的不必要的写入,降低存储速度。

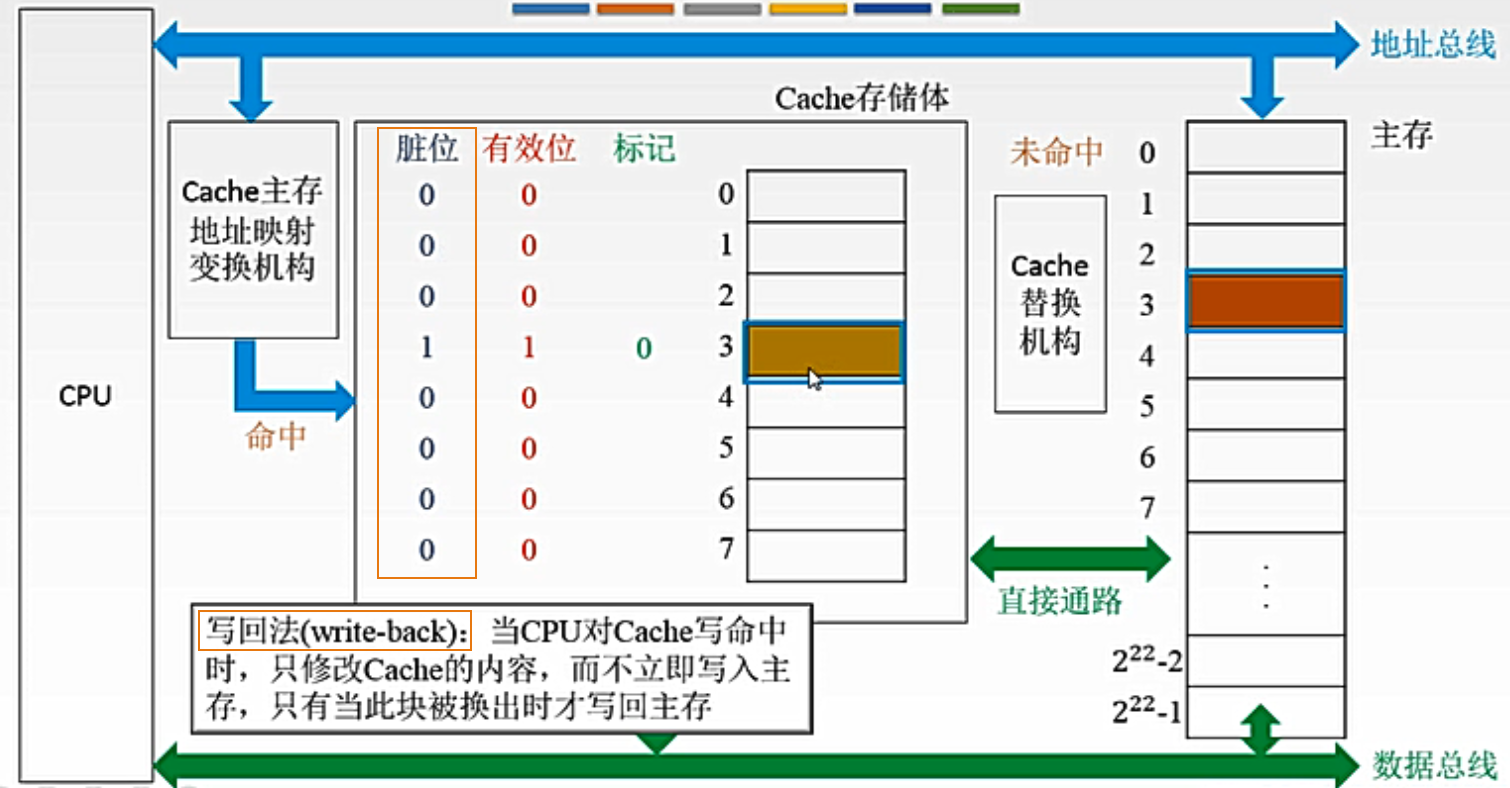

2. 写回法

Cache,不写入主存。仅当需要替换时,才把已经修改过的Cache块写回主存。

- 增加一个

被修改后的标记位1,如果替换时的块的标志位为1,则需要同步主存;若为0,则直接覆盖Cache旧的块。

缓存不命中时

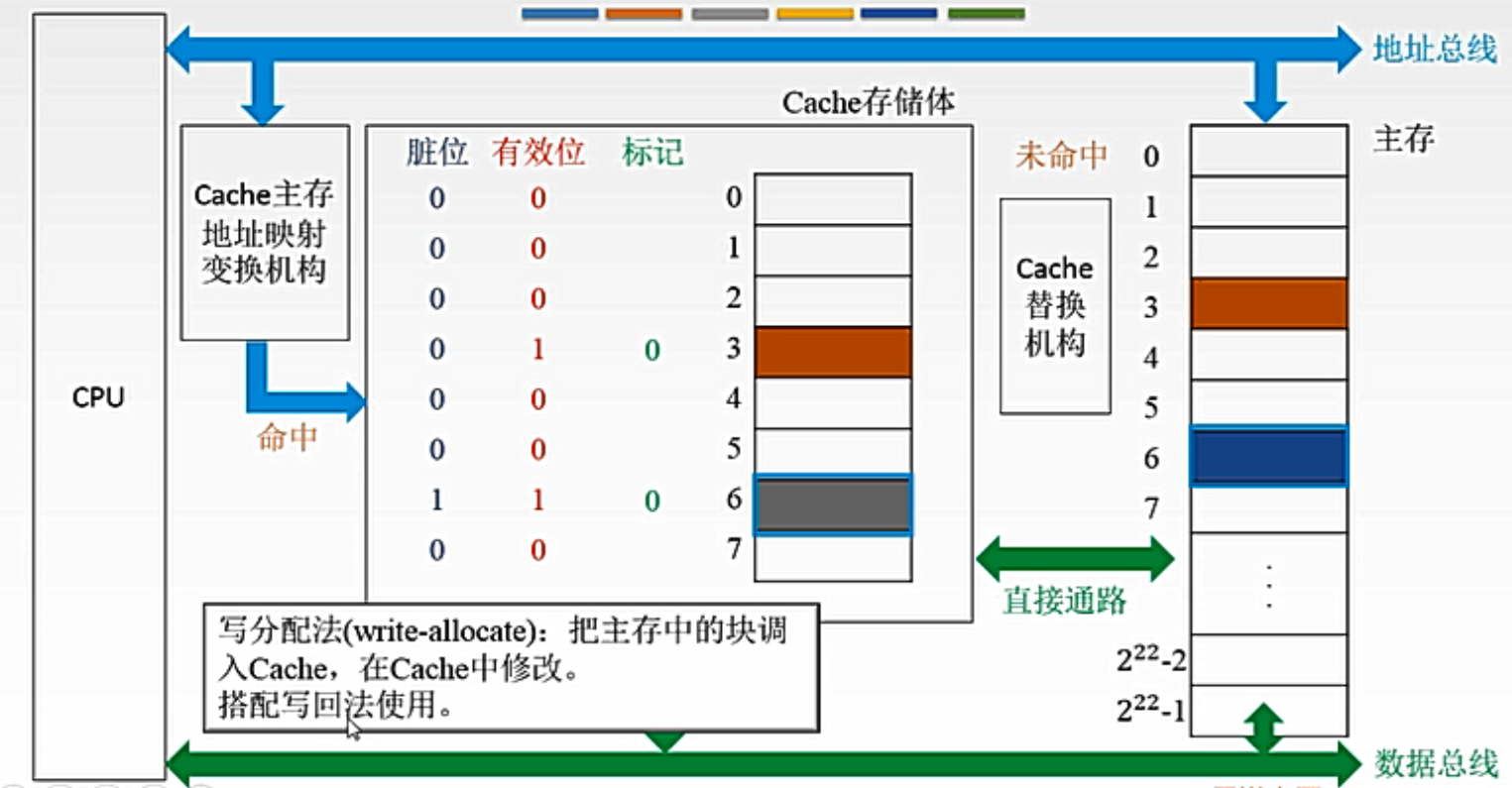

1. 写分配法

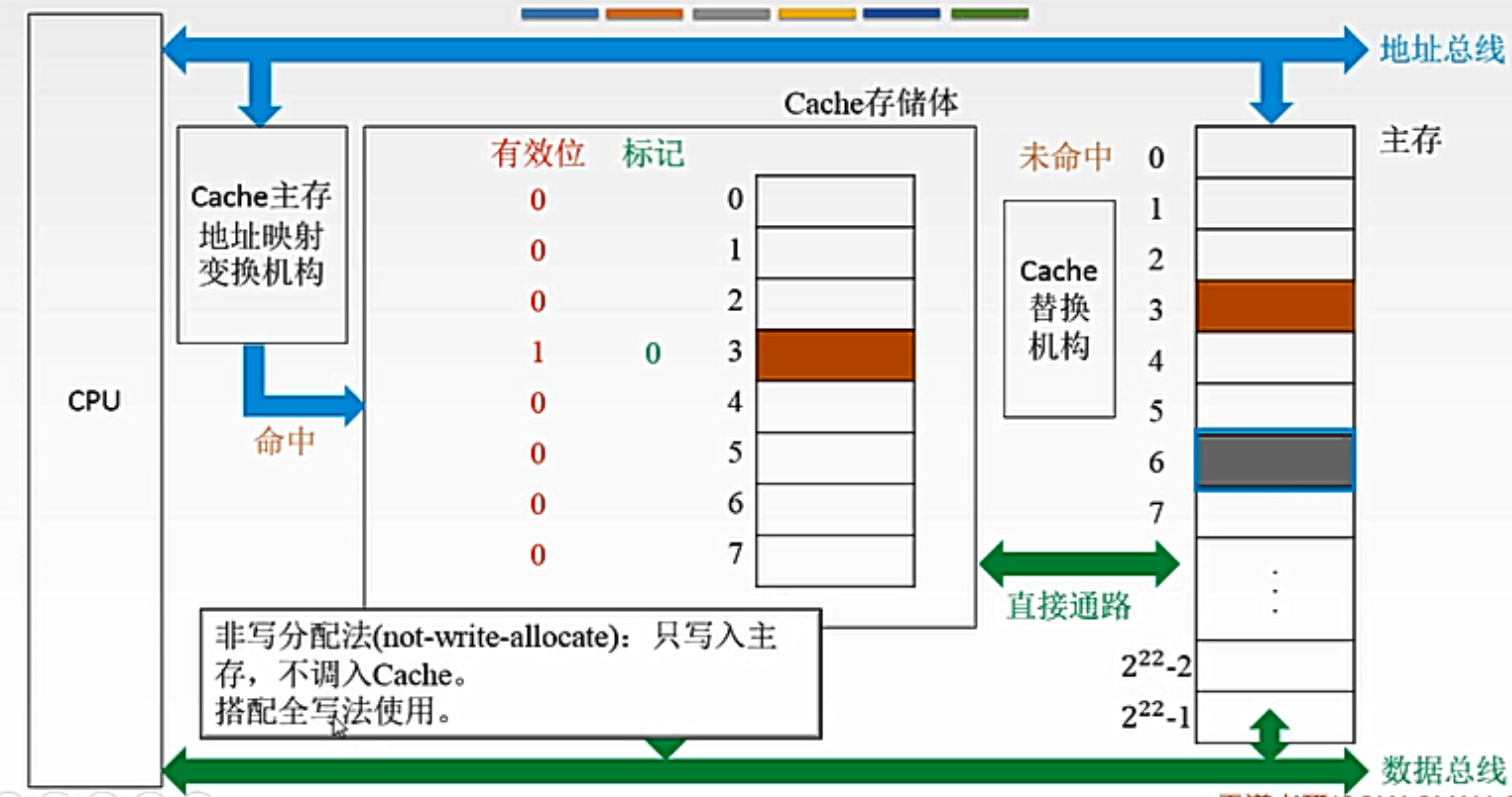

2. 非写分配法

5.7.5 总结

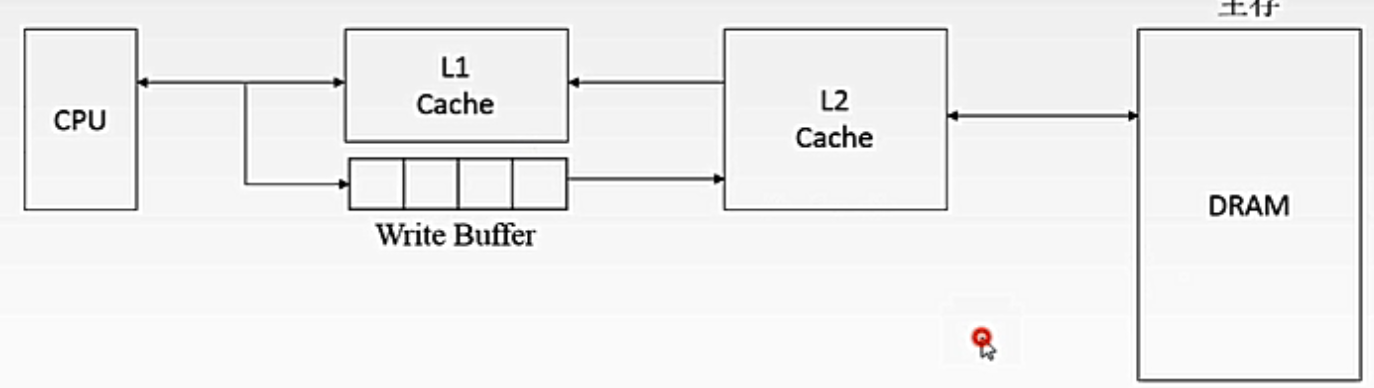

(5.7.6) PC中Cache技术的实现

1. 单一缓存和多级缓存

2. 统一缓存和分开缓存

- 统一缓存:指令、数据放到一个Cache

- 分开缓存:指令Cache和数据Cache

附:Cache的工作原理

附:Cache的总容量可以看3.6.4.

题型有

5.7 总结