本文对学习内容做一个记录,方便后期对知识点复习和补充。

课程:计算机组成原理、操作系统、计算机网络

计算机总线

总线的概述

总线的例子

- USB:通用串行总线(Universal Serial Bus)

- 提供了对外连接的接口

- 不同设备可以通过USB接口进行连接

- 连接的标准,促使外围设备接口的统一

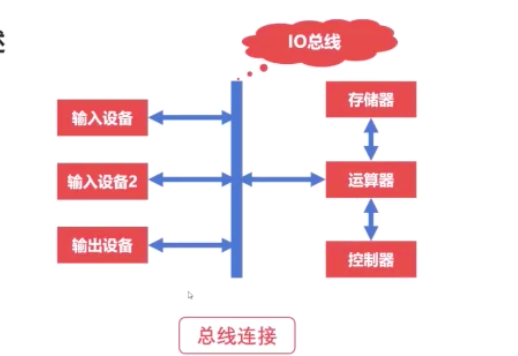

- PCI总线:外置显卡插在此处

- ISA总线

- ThunderBolt总线(苹果电脑的总线)

总线的作用

- 总线是为解决不同设备之间的通信问题

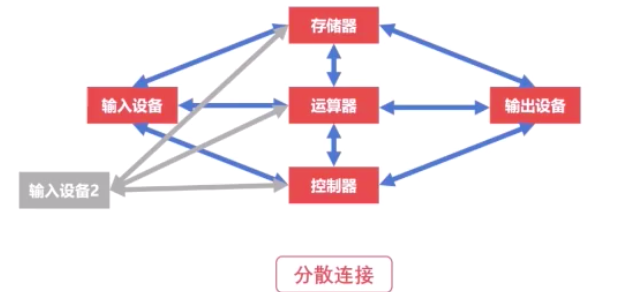

- 没有总线

- 有总线

总线的分类

片内总线

- 芯片内部的总线

- 可连接寄存器与寄存器、寄存器与控制器、运算器等

- 高集成度芯片内部的信息传输线,大大简化芯片内的电路结构

系统总线

- 连接计算机各种设备的总线

数据总线

- 双向传输各个部件的数据信息

- 数据总线的位数(总线宽度)是数据总线的重要参数,一般与CPU位数相同

地址总线

- 指定源数据或目的数据在内存中的地址,如果地址总线位数=n,则寻址范围为0~2^n

- 地址总线的位数与存储单元有关

控制总线

- 控制总线是用来发出各种控制信号的传输线

- 控制信号经由控制总线从一个组件发给另外一个组件

- 控制总线可以监视不同组件之间的状态(就绪/未就绪)

总线的仲裁

为什么需要总线的仲裁?

- 假设主存需要和硬盘、I/O设备交换数据,硬盘和I/O设备均已准备就绪,总线应该由哪个使用,需要仲裁器解决这个矛盾问题,否则会引起设备之间的冲突

- 仲裁器是为了解决总线使用权的冲突问题

总线的仲裁方法

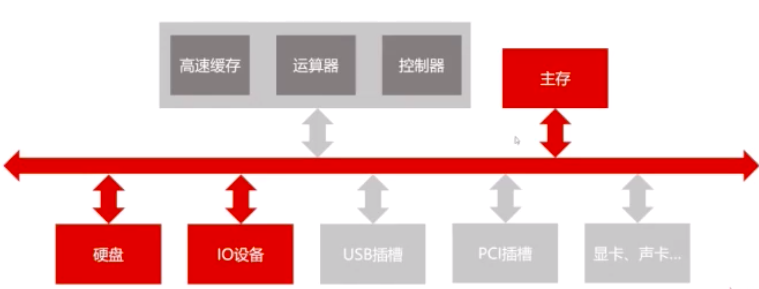

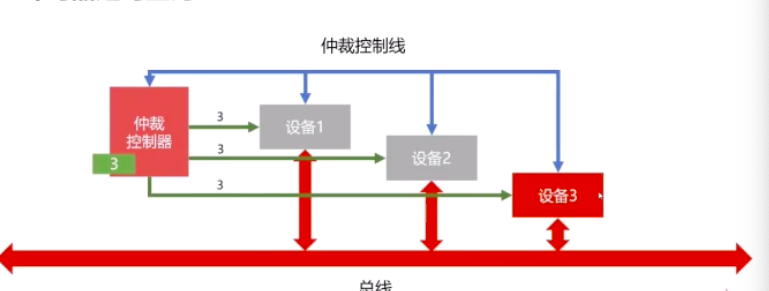

链式查询

- 假设设备2需要使用总线,设备2通过仲裁控制线向仲裁控制器发送总线使用的请求

- 仲裁控制器接收到请求后,发出允许使用的信号

- 信号会通过链式优先进入设备1,如果设备1不需要使用的话,会进入设备2,设备2拿到信号后就可以使用总线

- 如果设备1和设备2均发送使用请求,则会按照链式顺序依次使用总线

链式查询的优缺点

- 好处:电路复杂度低,仲裁方式简单

- 坏处:

- 优先级低的设备难以获得总线的使用权

- 对电路的故障敏感

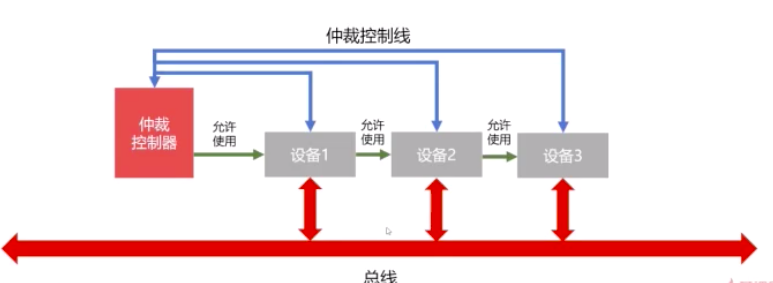

计时器定时查询

- 仲裁控制器对设备编号并使用计数器累计计数

- 接收到仲裁信号后,往所有设备发出当前计数值

- 计数值与设备编号一致则获得总线使用权

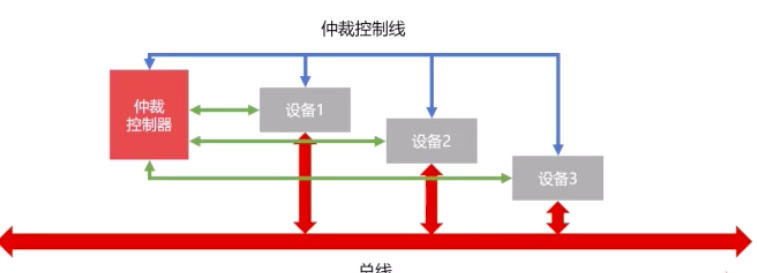

独立请求

- 每个设备均有总线独立连接仲裁器

- 设备可单独向仲裁器发送请求和接收请求

- 当同时收到多个请求信号,仲裁器有权按照优先级分配使用权

独立请求的优缺点

- 好处:响应速度快,优先顺序可动态改变

- 坏处:设备连线多,总线控制复杂

计算机的输入输出设备

常见的输入输出设备

字符输入设备:键盘

- 薄膜键盘

- 机械键盘

图形输入设备

- 鼠标

- 数位板:输入板和压感笔,常用于绘图设计创作

- 扫描仪:将图形信息转换为数字信号

图像输出设备

- 显示器

- 打印机

- 投影仪

输入输出接口的通用设计

数据线

- 是I/O设备与主机之间进行数据交换的传送线

- 单向传输数据线

- 双向传输数据线

状态线

- I/O设备状态向主机报告的信号线

- 查询设备是否已经正常连接并就绪

- 查询设备是否已经被占用

命令线

- CPU向设备发送命令的信号线

- 发送读写信号

- 发送启动停止信号

设备选择线

- 主机选择I/O设备进行操作的信号线

- 对连在总线上的设备进行选择

CPU与I/O设备的通信

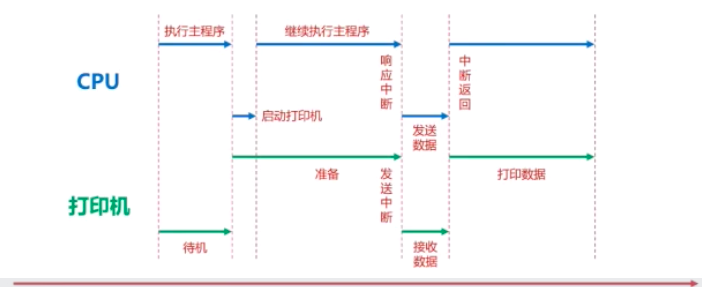

程序中断

- 当外围I/O设备就绪时,向CPU发出中断信号

- CPU有专门的电路响应中断信号,响应中断不会立即执行,有一定的响应时间

- 程序中断提供低速设备通知CPU的一种异步方式

- CPU可以高速运转同时兼顾低速设备的响应,如果频繁打断CPU,会降低CPU使用效率

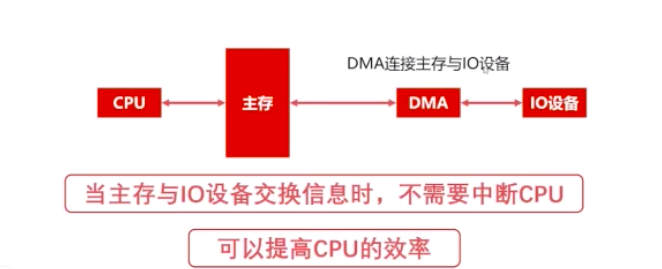

DMA(直接存储器访问)

- DMA直接连接主存与I/O设备

- DMA工作时不需要CPU参与

计算机存储器概览

存储器的分类

按存储介质分类

- 半导体存储器

- 内存

- U盘

- 固态硬盘

- 磁存储器

- 磁带

- 磁盘

按存取方式分类

- 随机存储器(RAM)

- 随机读取

- 与位置无关

- 串行存储器

- 与位置有关

- 按顺序查找

- 只读存储器(ROM)

- 只读不写

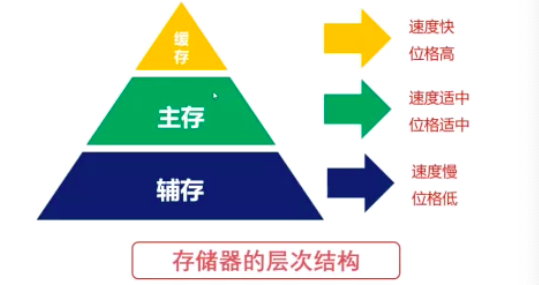

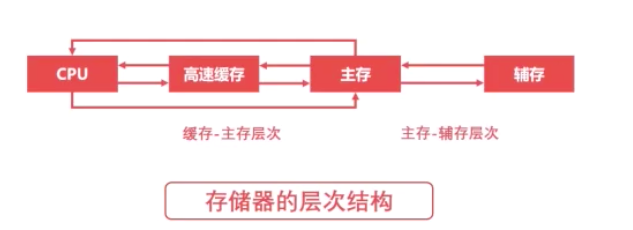

存储器的层次结构

- 容量+价格=>位价:每比特位价格

缓存-主存层次

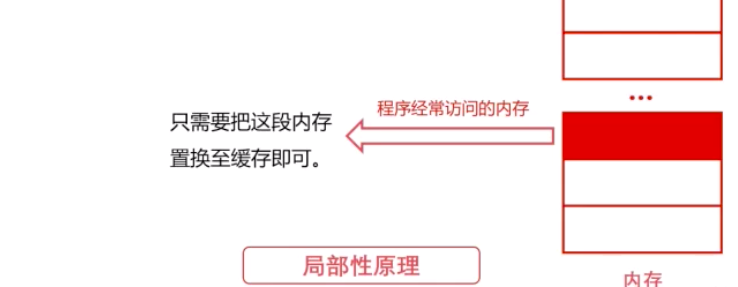

- 原理:局部性原理

- 局部性原理是指CPU访问存储器时,无论是存取指令还是存取数据,所访问的存储单元都趋于聚集在一个较小的连续区域中

- 局部性原理是指CPU访问存储器时,无论是存取指令还是存取数据,所访问的存储单元都趋于聚集在一个较小的连续区域中

- 实现:在CPU与主存之间增加一层速度快(容量小)的Cache

- 目的:解决主存速度不足的问题

主存-辅存层次

- 原理:局部性原理

- 实现:主存之外增加辅助存储器(磁盘、SD卡、U盘等)

- 目的:解决主存容量不足的问题

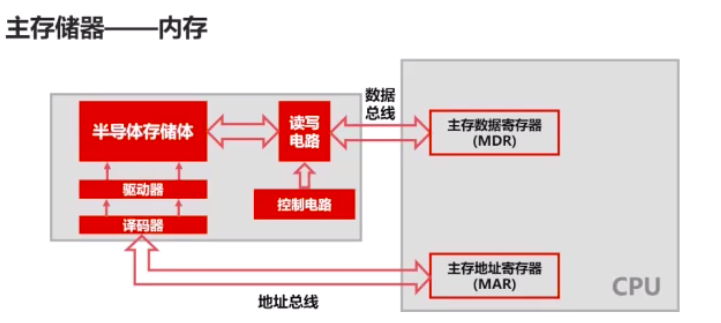

计算机的主存储器与辅助存储器

主存储器--内存

- RAM(随机存取存储器:Random Access Memory)

- RAM通过电容存储数据,必须隔一段时间刷新一次

- 如果断电,那么一段时间后将丢失所有数据

- 32位系统:最多只能支持4GB内存,因为地址总线只有32位,即2^32 = 4 x 2^30 = 4GB

- 64位系统:最多能支持2^34GB内存,即2^64 = 2^34 x 2^30 = 2^34GB

辅助存储器--磁盘

- 表面是可磁化的硬磁特性材料

- 移动磁头径向运动读取磁道信息

磁盘的调度算法

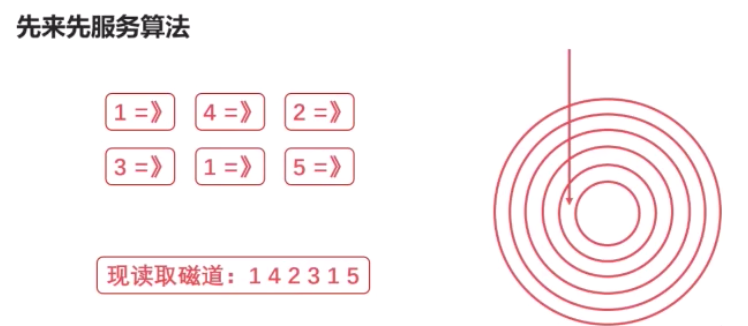

- 先来先服务算法

- 按顺序访问进程的磁道读写需求

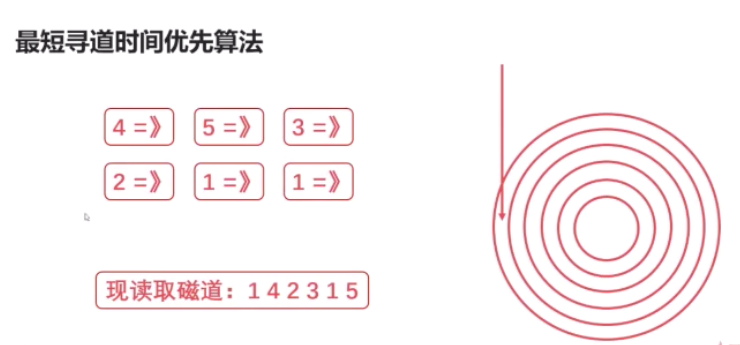

- 最短寻道时间算法

- 与磁头当前的位置有关

- 优先访问离磁头最近的磁道

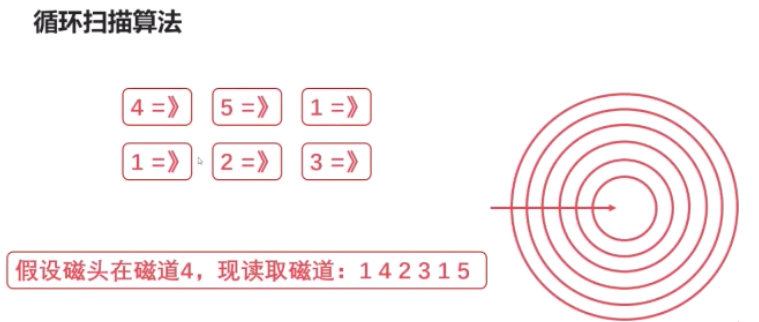

- 扫描算法(电梯算法)

- 每次只往一个方向运动

- 到达一个方向需要服务的尽头再反方向移动

- 循环扫描算法

计算机的高速缓存

高速缓存的工作原理

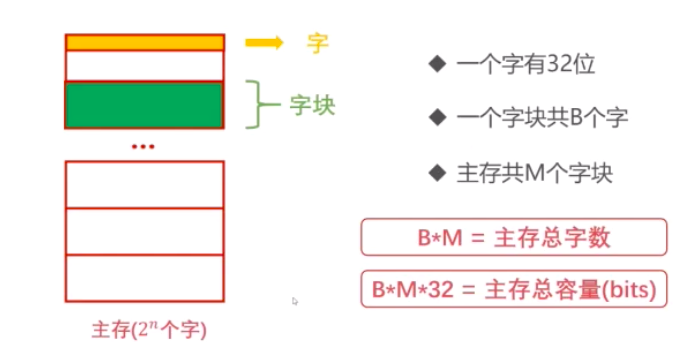

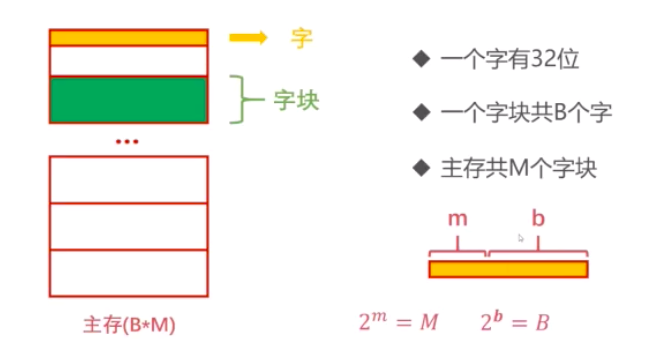

- 字:是指存放在一个存储单元中的二进制代码组合

- 字块:存储在连续的存储单元中被看做是一个单元的一组字

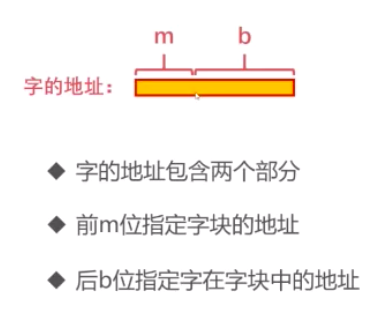

主存的存储结构

- 假设一个字有32位

字的地址表示:

缓存的存储结构

- 缓存和主存存储的逻辑结构类似

- 缓存的容量较小

- 缓存的速度更快

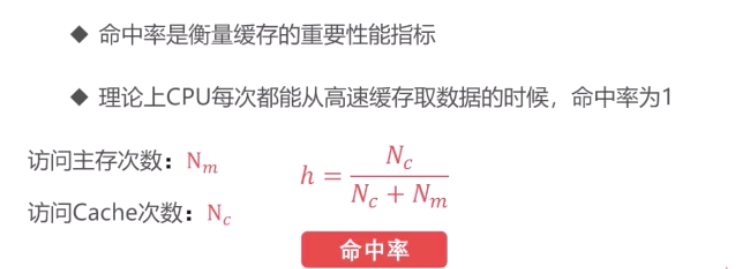

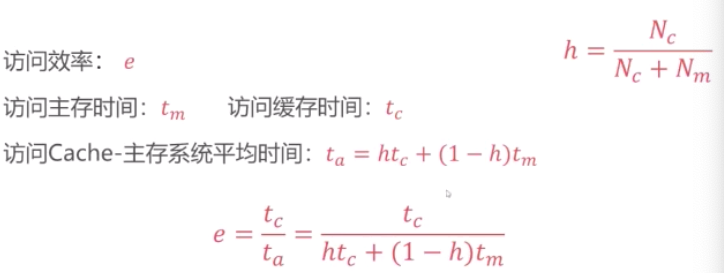

缓存的性能指标

- 命中率

- 访问效率

高速缓存的替换策略

- 高速缓存的替换时机,缓存中没有数据,需要从主存载入所需数据

高速缓存的替换策略

- 随机算法

- 先进先出算法(FIFO)

- 把高速缓存看做是一个先进先出的队列,优先替换最先进入队列的字块

- 最不经常使用算法(LFU)

- 优先淘汰最不经常使用的字块

- 需要额外的空间记录字块的使用频率

- 最近最少使用算法(LRU)

- 优先淘汰一段时间内没有使用的字块

- 有多种实现方法,一般使用双向链表

- 把当前访问节点置于链表前面(保证链表头结点是最近使用的)

- 需要淘汰的话就在链表尾部去掉就好了

计算机的指令系统

机器指令的形式

- 机器指令主要由两部分组成:操作码字段、地址码字段

操作码字段

- 操作码指明指令所要完成的操作

- 操作码的位数反映了机器的操作种类,比如操作码有8位,则最多就有2^8 = 256种操作

地址码字段

- 地址码直接给出操作数或者操作数的地址

- 分三地址指令、二地址指令和一地址指令

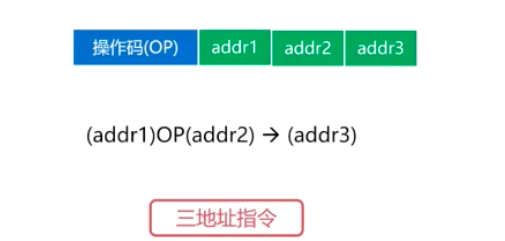

- 三地址指令

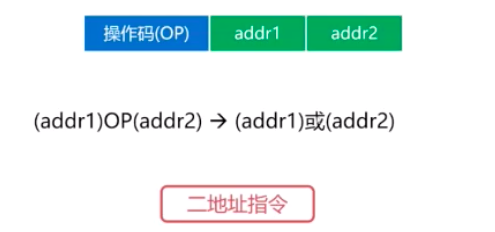

- 二地址指令

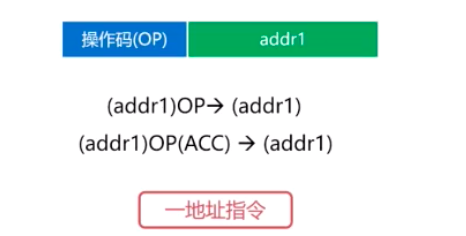

- 一地址指令

- 零地址指令,在机器指令中无地址码,即空操作、停机操作、中断返回操作等

- 三地址指令

机器指令的操作类型

数据传输

- 寄存器之间、寄存器与存储单元、存储单元之间传送(存储单元可以是主存,高速缓存或者辅存)

- 数据读写、交换地址数据、清零置一等操作

算术逻辑操作

- 操作数之间的加减乘除运算

- 操作数的与或非等逻辑位运算

移位操作

- 数据左移(乘2)、数据右移(除2)

- 完成数据在算术逻辑单元的必要操作

控制指令

- 等待指令、停机指令、空操作指令、中断指令等

机器指令的寻址方式

指令寻址

- 顺序寻址

- 跳跃寻址

数据寻址

- 立即寻址:指令直接获得操作数,无需访问存储器

- 直接寻址:直接给出操作数在主存的地址,寻找操作数简单,无需计算数据地址

- 间接寻址:指令地址码给出的是操作数地址的地址,需要访问一次或多次主存来获取操作数

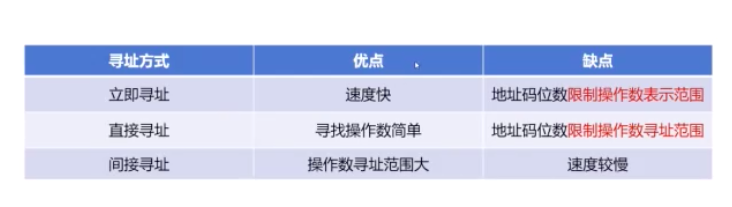

三种数据寻址的优缺点

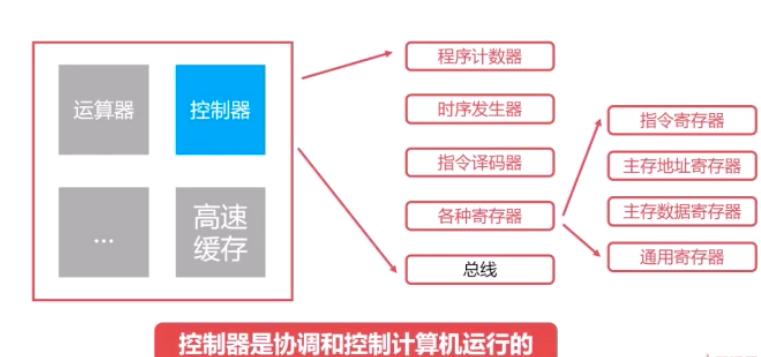

计算机的控制器

程序计数器

- 程序计数器用来存储下一条指令的地址

- CPU会循环从程序计数器中拿出指令

- 当指令被拿出时,指向下一条指令

时序发生器

- 电气工程领域,用于发送时序脉冲

- CPU依据不同的时序脉冲有节奏的进行工作

指令译码器

- 指令译码器是控制器的主要部件之一

- 计算机指令由操作码和地址码组成

- 翻译操作码对应的操作以及控制传输地址码对应的数据

指令寄存器

- 指令寄存器是控制器的主要部件之一

- 缓存从主存或高速缓存取的计算机指令

主存地址寄存器

- 保存当前CPU正要访问的内存单元的地址

主存数据寄存器

- 保存当前CPU正要读或写的主存数据

通用寄存器

- 用于暂时存放或传送数据或指令

- 可保存ALU(算术逻辑单元)的运算中间结果

- 容量比一般专用寄存器要大

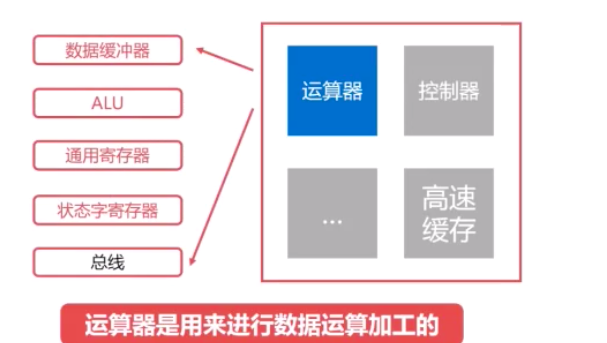

计算机的运算器

数据缓冲器

- 分为输入缓冲和输出缓冲

- 输入缓冲暂时存放外设送过来的数据

- 输出缓冲暂时存放送往外设的数据

ALU

- ALU:算术逻辑单元,是运算器的主要组成

- 常见的位运算(左右移,与或非等)

- 算术运算(加减乘除等)

状态字寄存器

- 存放运算状态(条件码、进位、溢出、结果正负等)

- 存放运算控制信息(调试跟踪标记为、允许中断位等)

通用寄存器

- 用于暂时存放或传送数据或指令

- 可保存ALU(算术逻辑单元)的运算中间结果

- 容量比一般专用寄存器要大