今天的RISC-V微控制器可能导致未来RISC-V手机和笔记本电脑的出现。

SiFive的 "Essential "系列被简化为标准微控制器职责所需的最低配置和性能。"智能 "系列增加了AI/ML加速,而新的 "性能 "系列则提供了它所标榜的功能。

今天,RISC-V CPU设计公司SiFive推出了一个有两个核心设计的新处理器系列。P270(完全支持RISC-V的向量扩展1.0候选版本的Linux能力的CPU)和P550(迄今为止性能最高的RISC-V CPU)。

RISC-V概述

对于那些不熟悉RISC-V的人来说,它是一个相对较新的CPU架构,利用了精简指令集计算机(RISC)的原理。RISC-V是一个开放的标准,专门设计成具有前瞻性,并尽可能地避免遗留问题。这种设计的一个例子是RISC-V的动态宽度矢量指令集,它允许开发人员以最大的效率在任意大小的数据上执行矢量指令。

在传统的处理器设计中,矢量指令有一个固定的宽度,与处理器的硬件寄存器大小相关--例如,SSE和SSE2允许使用奔腾III的128位寄存器,而充分利用i7-4770的256位寄存器需要一个完全独立的指令集(AVX2)进行相同的数学操作。升级到i7-1065G7的512位寄存器需要另一个指令集,即AVX-512--再次用于相同的基本数学操作。

与此形成鲜明对比的是,RISC-V矢量数学允许一组CPU指令尽可能有效地执行相同的数学运算,使用当前CPU设计中可用的任何大小的寄存器。这意味着开发者只需编写一个例程,就可以在拥有64位寄存器的手机或拥有1024位寄存器的超级计算机上尽可能有效地处理矢量运算。

除了RISC-V规范中内置的前瞻性功能外,该架构还旨在提供其设计者没有或无法提前想到的灵活性。通用的RISC-V设计具有保留的操作代码,特定RISC-V CPU的设计者可以接管这些代码,以提供额外的、任意的功能。

"接管 "预留操作码的能力可以大大简化ASIC设计,因为专门的指令和一般的控制器功能都可以在一个芯片上提供,而且CPU架构师不需要重新发明任何轮子来提供通用控制器功能。

目前,在通用处理器领域,RISC-V不是Arm或x86的严重竞争对手,但它在微控制器领域被大量使用,部分原因是其可扩展性和廉价的许可。我们广泛期待RISC-V在通用CPU方面成为第三个主要参与者--为手机、平板电脑和传统计算机提供 "主脑 "的那种--但这仍然是一些未来需要持续探索的事。

SiFive高性能系列有什么新产品?

今天宣布的两个新设计是P270和P550。P270是SiFive第一个完全支持可选的RISC-V矢量扩展1.0候选版本的CPU,而P550是SiFive迄今为止性能最高的RISC-V处理器--也使其成为我们所知的性能最高的RISC-V处理器。

P270和 "V "1.0-rc1

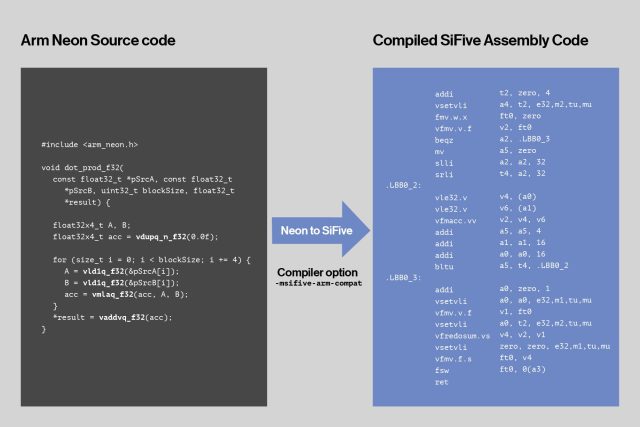

SiFive的Recode自动将传统的SIMD源代码翻译成SiFive矢量汇编--在这种情况下,从为Arm的Neon指令集编写的源代码开始。

正如你对 "候选发布 "的期望,RISC-V的 "V "可选指令集还不是一个冻结的标准。当V规格达到1.0时--没有 "候选发布 "指令--它将被认为是稳定的,足以冻结该功能集。这将允许开发者开始长期项目的工作,将其用于工具链、功能模拟器等等,并在一定程度上确定开发者编写的代码将在未来的CPU设计上 "正常工作"。

值得注意的是,即使取消了候选发布版的标签,1.0版本的V指令仍将只被认为是准备好供公众批准的。V的第一个真正的生产版本将是2.0,这个版本号是在公众批准被认为完成后授予的,没有必要进行重大功能改变。

SiFive还提供了一个名为Recode的翻译工具,可以自动将传统的SIMD代码转换为V-spec向量汇编。

P550高性能

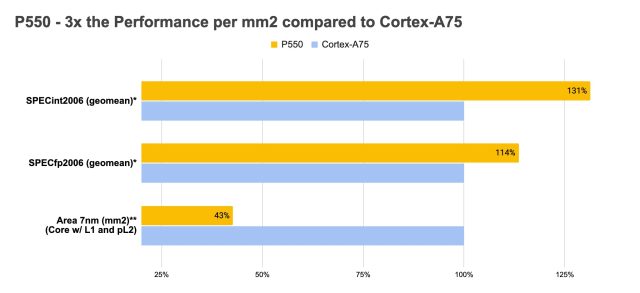

这个有点混乱的柱状图显示,单个P550内核的性能明显优于同等的Cortex A75内核(上两图),同时在每片平方毫米的性能上将其吹得一塌糊涂(下图)。

P270和P550都是支持Linux的设计,但P270被限制在一个只有八级的双发内序流水线。虽然P270的全V扩展支持应使其成为严重依赖矢量数学应用的强大处理器,但P550应证明在接近目前由通用CPU处理的应用方面要强大得多。

SiFive新的Performance P550内核具有13级、三发、失序流水线。SiFive称,基于P550的四核CPU所占的片上面积与单个Arm Cortex-A75大致相同,与Arm的竞争性设计相比,性能优势明显。SiFive称,根据内部工程测试结果,P550每GHz可提供8.65个SPECInt 2006,与Cortex-A75相比,这是一个值得称赞的结果(与i9-10900K的11.08/GHz相比也相差不远)。但它远远落后于苹果A14的21.1/GHz。

英特尔采用P550用于其Horse Creek平台

首先,我们需要明确一点--我们几乎肯定不是在谈论英特尔放弃x86_64架构而采用RISC-V的问题英特尔和AMD的现代x86_64 CPU包括管理和监督内核,最终用户不能直接访问。这些通常是Arm CPU内核;例如,AMD的第一个APU使用Cortex-A5作为其平台安全处理器。

英特尔和SiFive的联合公告并不清楚Horse Creek将是什么。英特尔通常将 "Creek "这个名字保留给插座式平台,而不是一体化的片上系统(SoC)板。这表明,在所有的可能性中,P550将被限制在x86_64 Horse Creek CPU的监督或管理职责,而不是直接处理运行在该平台上的软件指令。

Anandtech的Ian Cuttress指出,将P550直接构建在Horse Creek--它将建立在英特尔最新的7纳米工艺节点上--可能为英特尔提供更简单的测试和更快速的新7纳米工艺本身的开发。