触发器

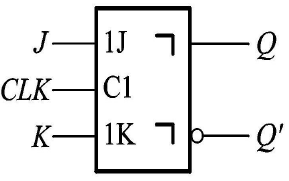

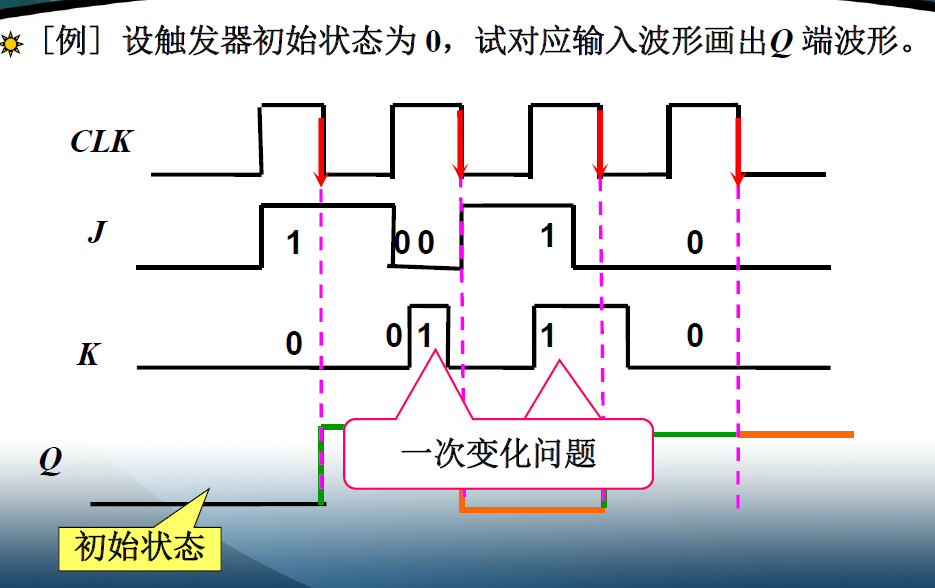

脉冲JK触发器

- 在clk下降沿到来得时候,看在clk=1内离下降沿最近的一次变化!

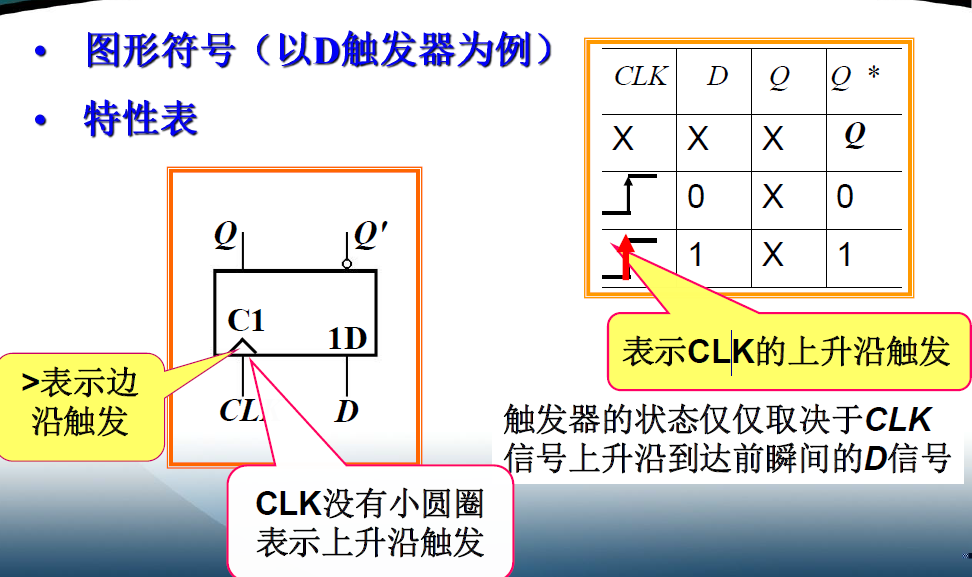

D触发器(边沿触发器)

- 触

发器的次态仅仅取决于CLK信号下降沿(或上升沿)到达

时刻输入信号的状态。

组合逻辑电路

八选一数据选择器

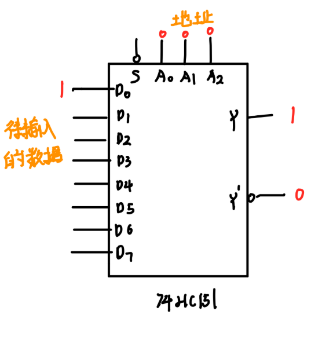

芯片图:

作用:需要八位数据输入和三位地址码,输出一位

真值表:

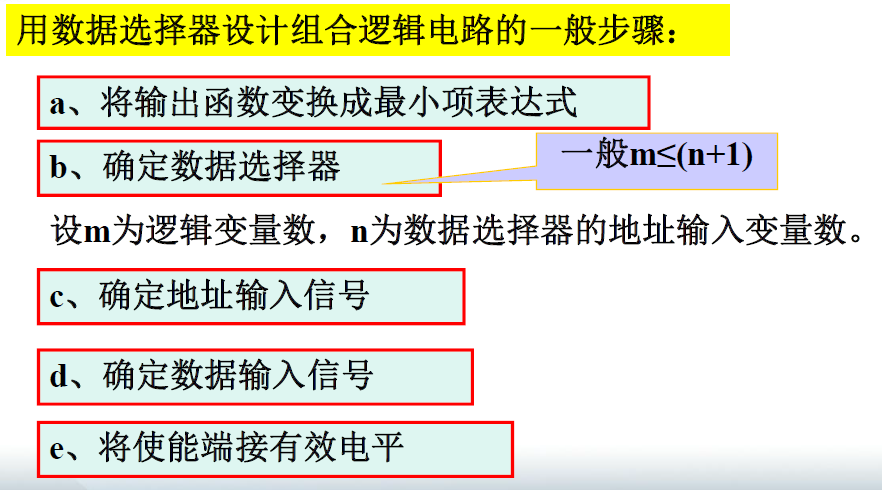

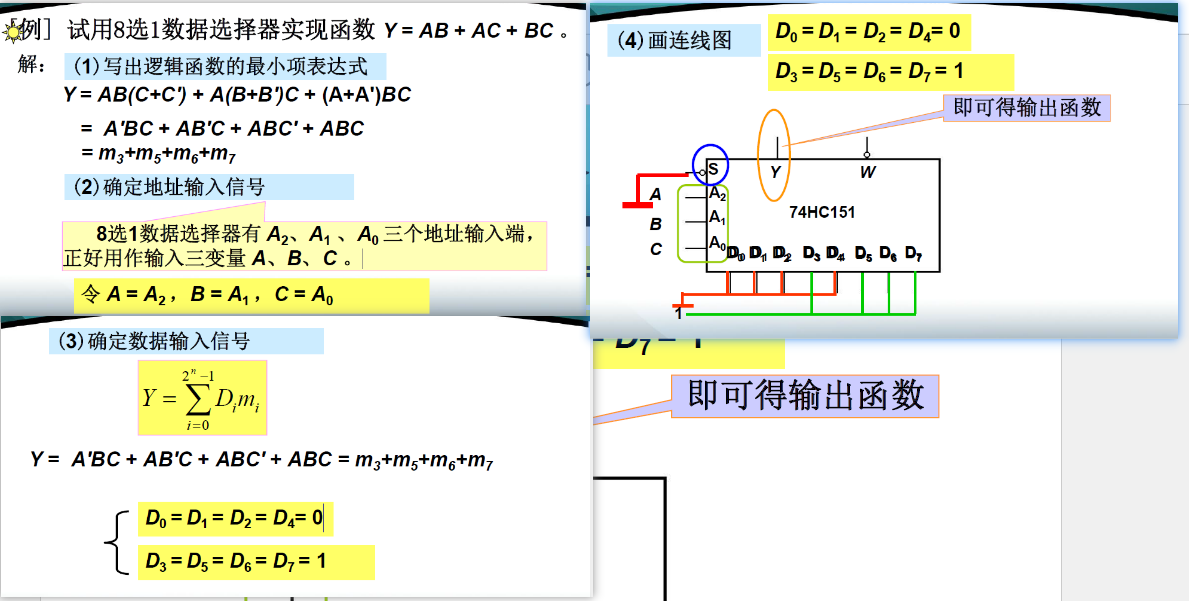

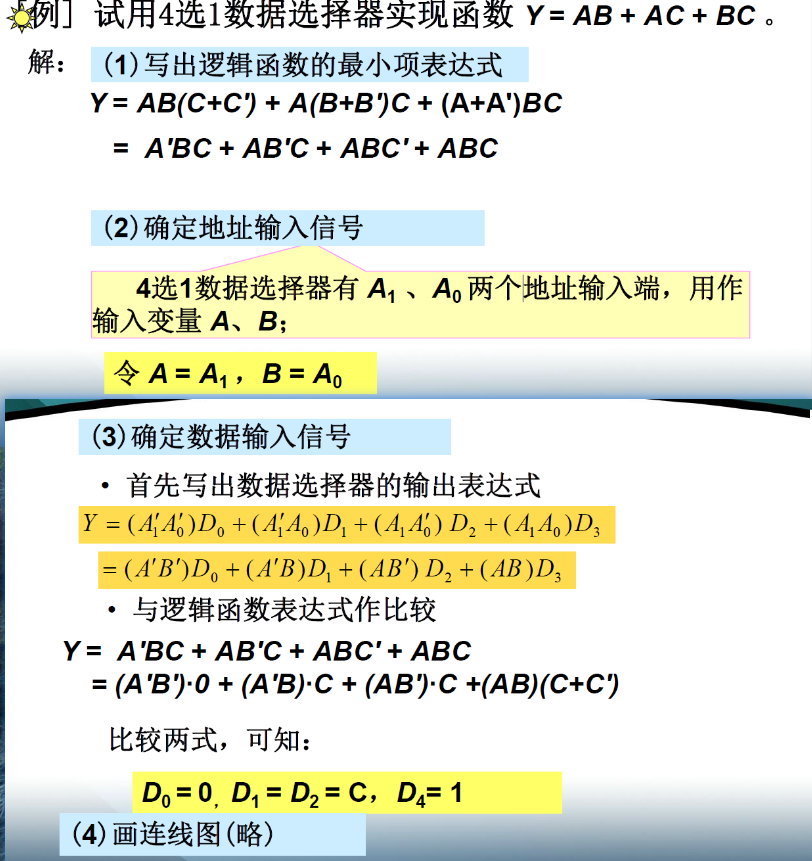

考题: 用数据选择器设计组合逻辑电路

关键:列出数据选择器的输出表达式和逻辑函数表达式进行对比

例题:

①当逻辑函数的变量个数和数据选择器的地址输入变量 个数相同时,可直接将逻辑函数输入变量有序地接数据 选择器的地址输入端。

②当逻辑函数的变量个数大于数据选择器的地址输入 变量个数时,Di可以当作变量来处理

时序逻辑电路

由触发器组成的时序逻辑电路分析步骤:

- 列出状态方程、输出方程

- 写出状态转换表

- 画出状态转换图

其他大芯片,如161/160则按照各自特点进行分析

计数器

10进制/16进制计数器

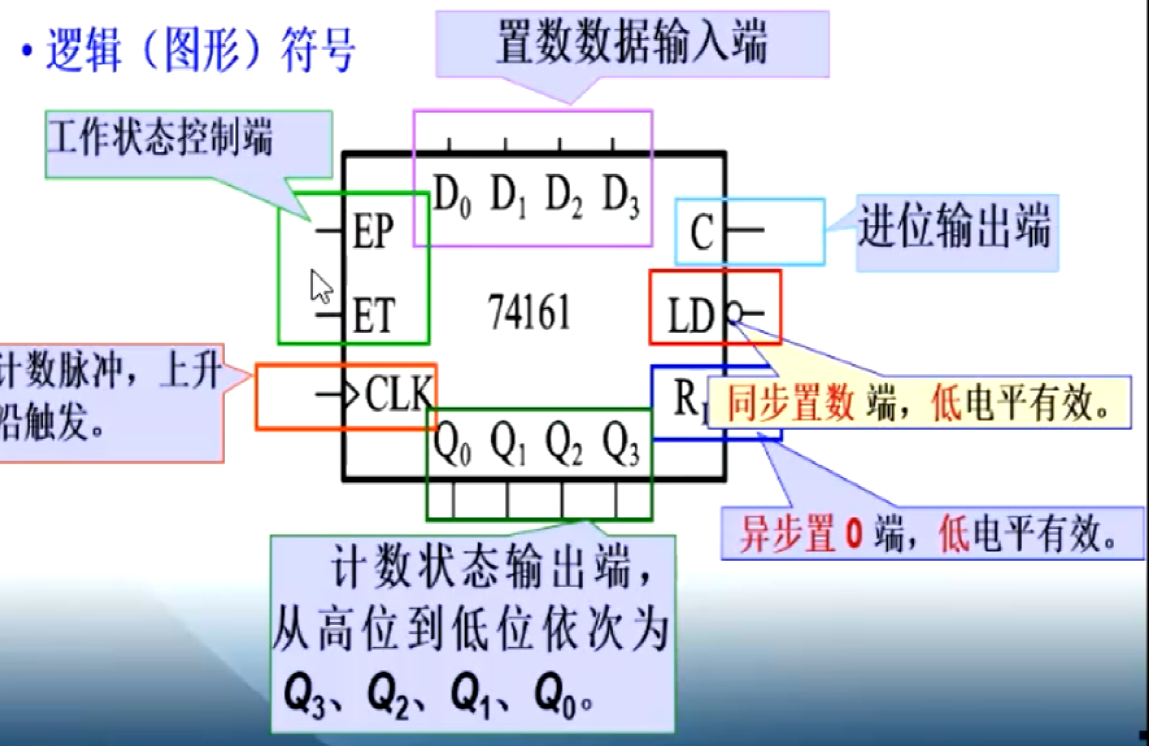

74161--16进制计数器芯片

74160--10进制计数器芯片

图:

功能表:

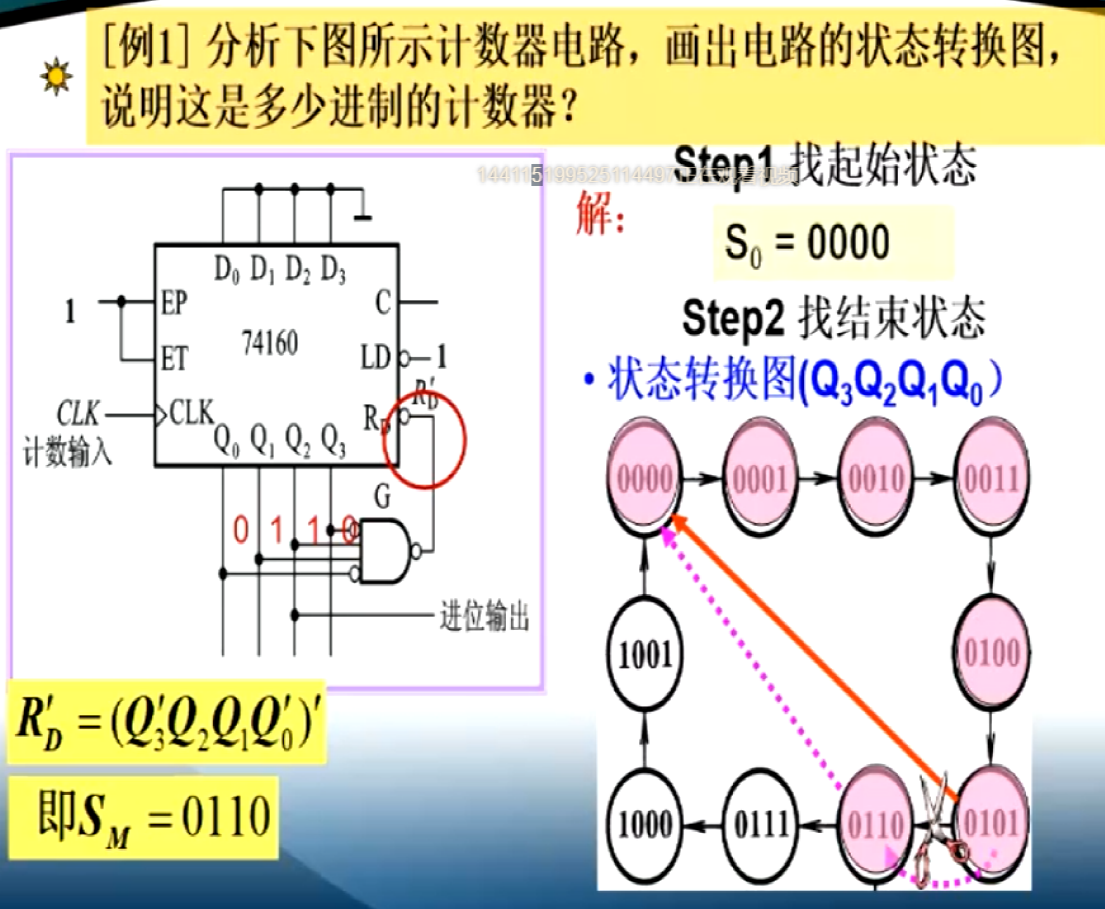

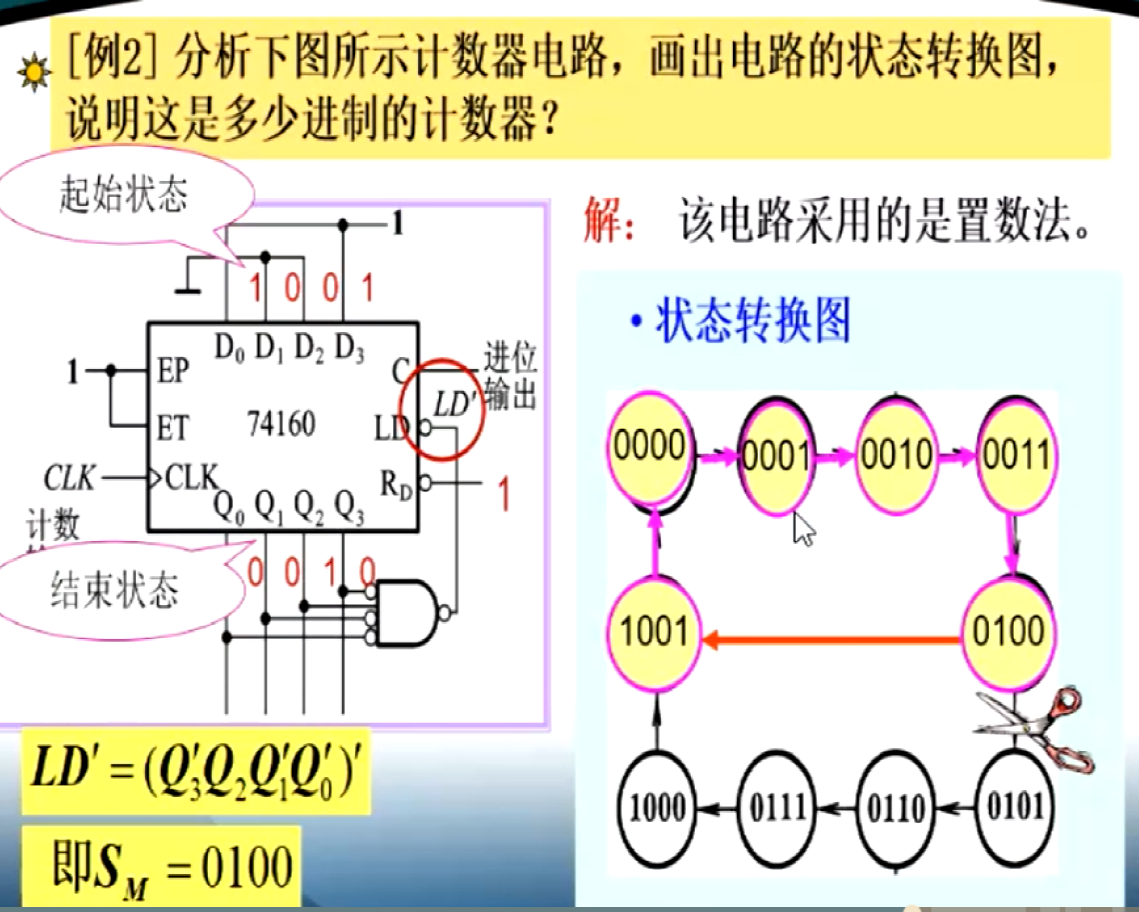

6进制计数器(N>M)

方法一:置零法

方法二:置数法

做题步骤:

- 确定起始状态

- 确定结束状态(置零法结束状态有蹊跷)

- 画状态转换图

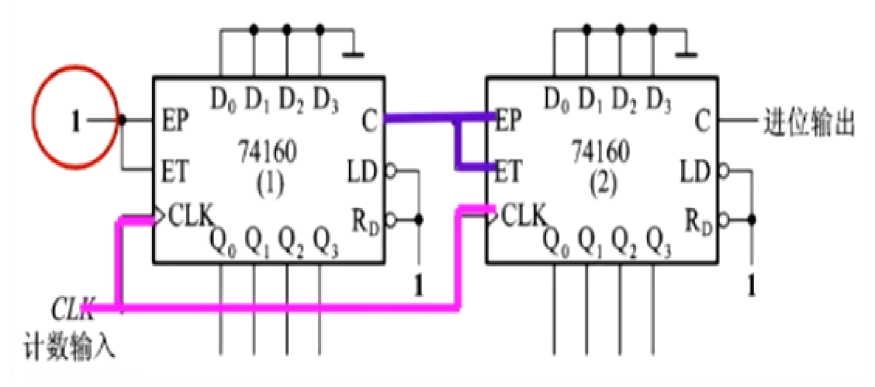

100进制计数器(N<M)/29进制计数器

①M=N1*N2

首先用前面的方法将两片集成计数器分别接成N1和N2两个计数器;然后,再将N1和N2两个计数器连接起来。 N1和N2之间的连接方式有两种:串行进位方式和并行进位方式。

【注】当N1进位后变为0000时,N2同时才变为0001;而不是N1处于最后一位时,N2就变了

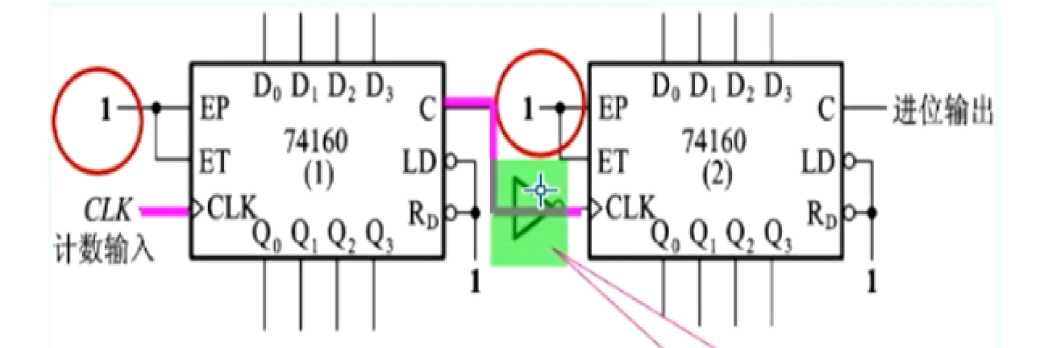

并行进位方式(同时工作,同一个CLK):

串行进位方式:

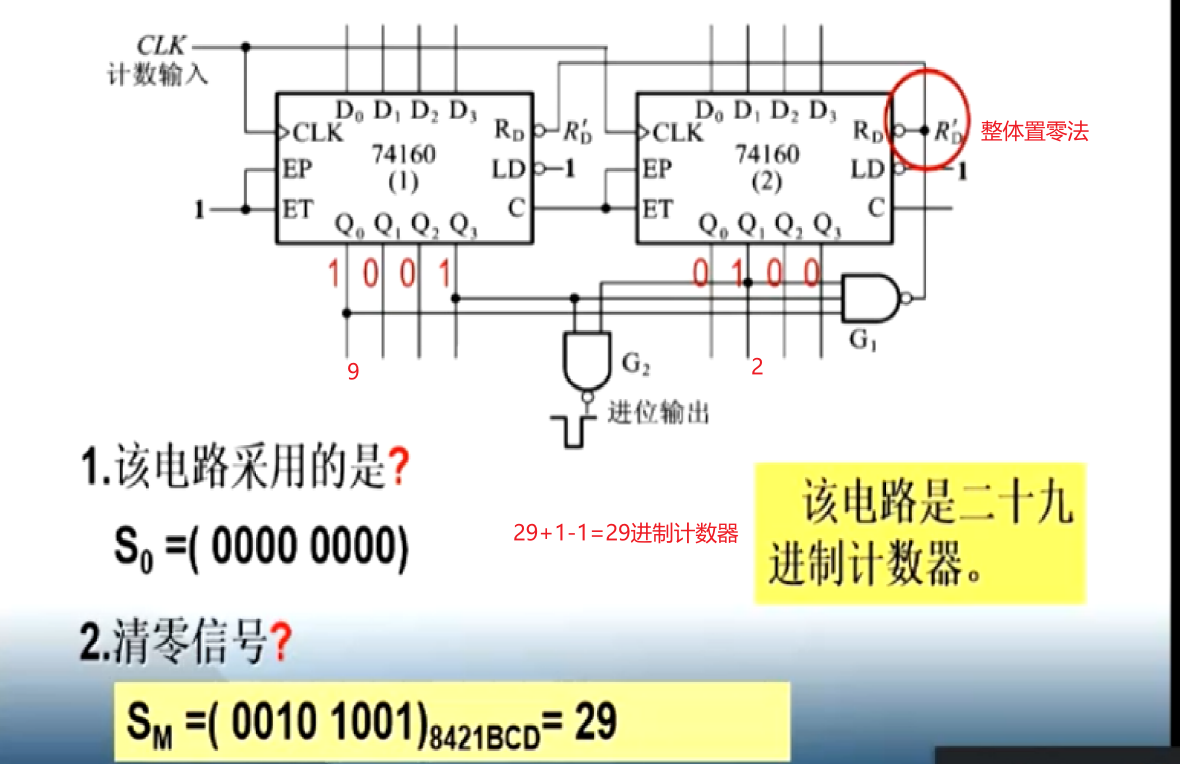

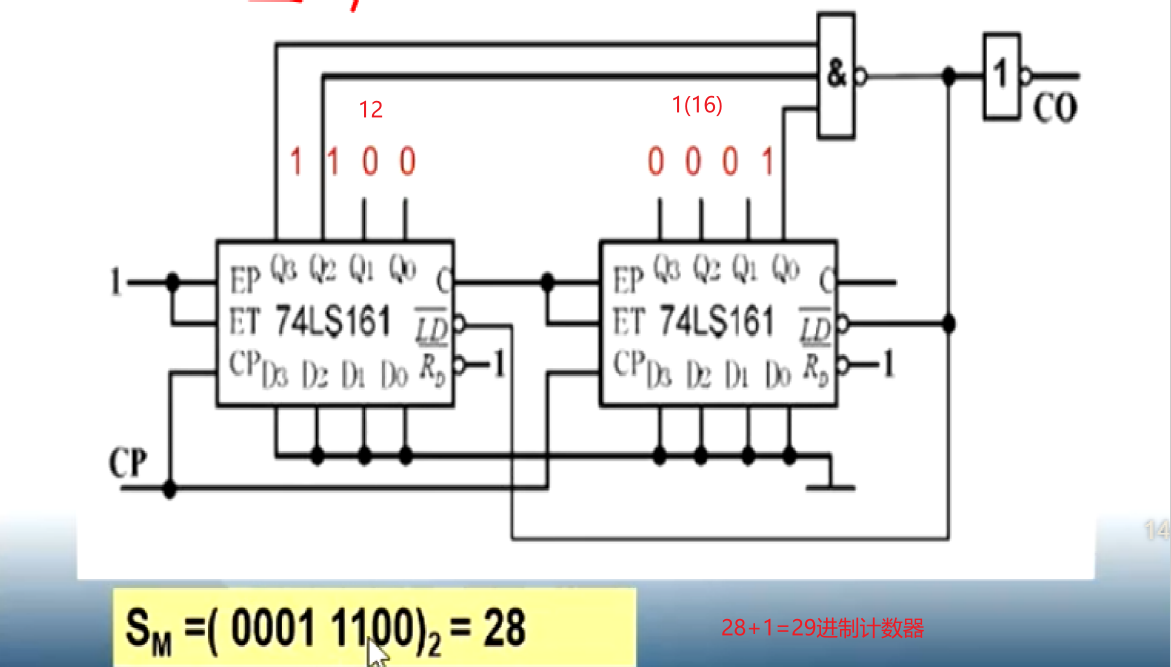

②M不分解为(N1xN2)时

此时先用多片N进制计数器接成一个大于M进制的计数器,然后再采用整体置零方式或整体置数方式构成M进制计数器,其原理与N<M的情况相同。

整体置零法:

整体置数法:

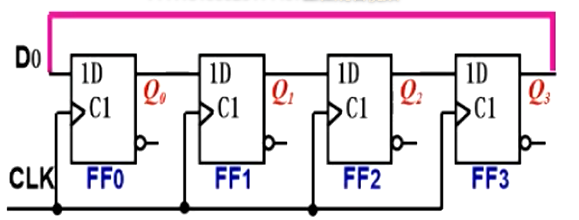

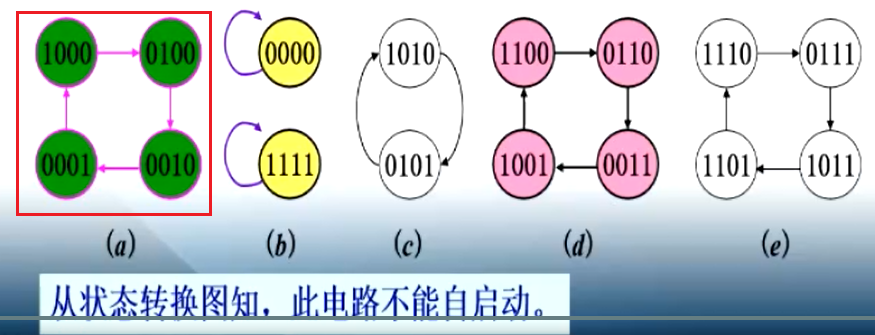

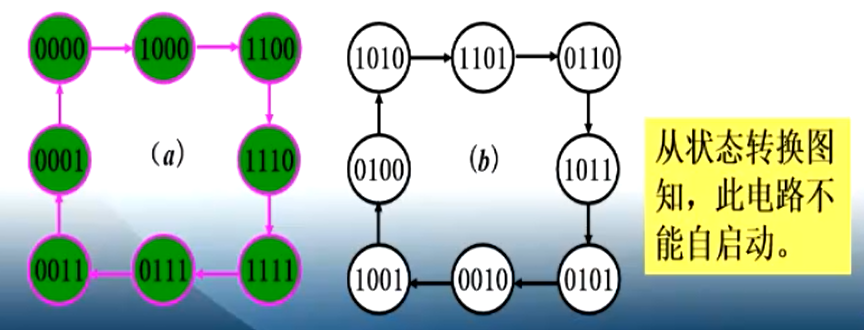

移位寄存器型计数器

环形计数器

图:

作用: 任意给定一个初始值,然后就将Q3扔到第一位,然后Q0Q1Q2右移一位,不断循环,达到计数的目的

缺点:状态利用率较低,上图中只利用了4个状态

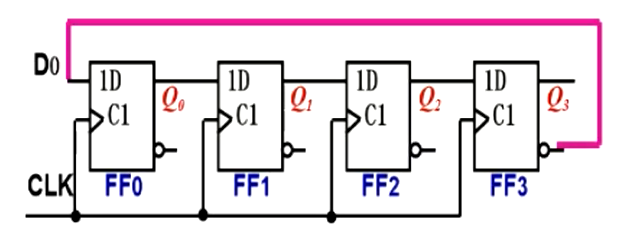

扭环形计数器(莫比乌斯环)

图:

状态转换图(Q0Q1Q2Q3):(按照时序逻辑电路分析步骤来获得)

作用: 任意给定一个初始值,然后就将Q3取反扔到第一位,然后Q0Q1Q2右移一位,不断循环,达到计数的目的

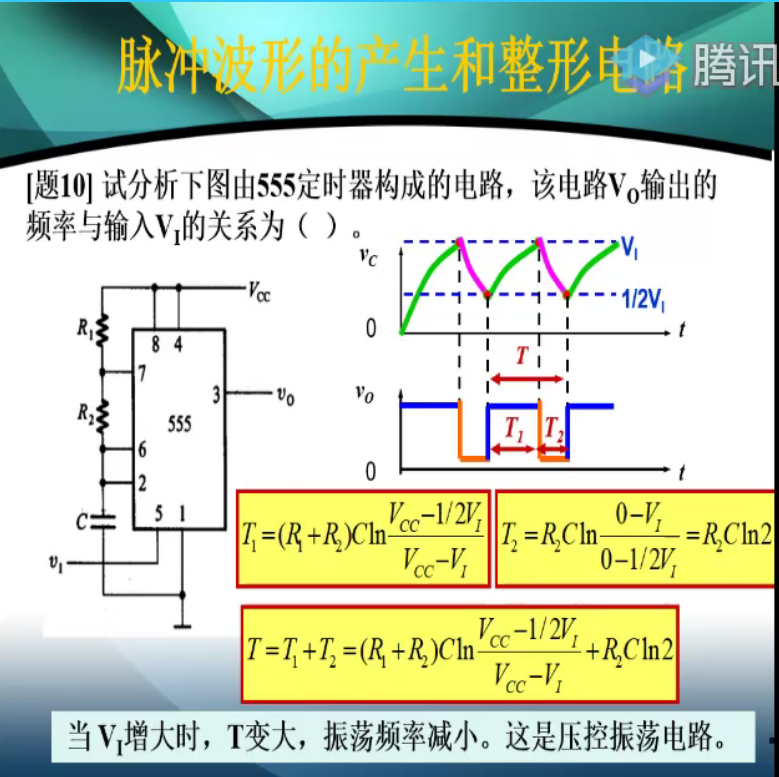

脉冲波形

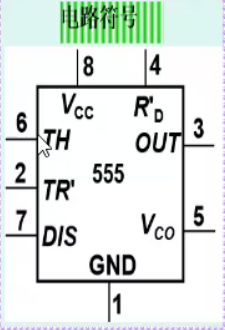

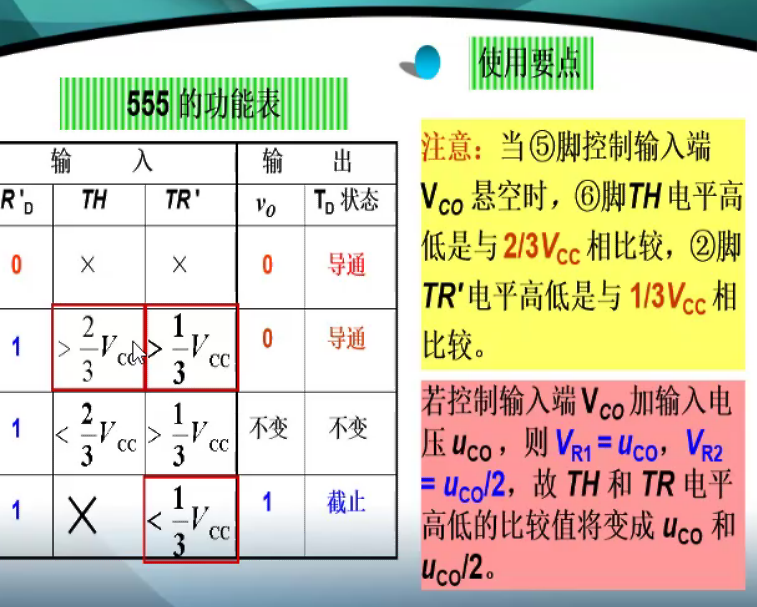

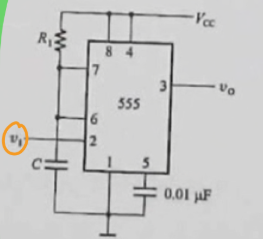

555定时器

特点:

- 1接地端;2,6是输入;3输出;4清零端;5控制电压端;7管子的输出端,放电端;8电源端

- 5可接控制电压

;悬空后,

,

;接了外接电压后,,

,

(

,

)

- 均大于各自的基准电压,输出为0,管子导通

- 处在两个基准电压之间,输出不变,管子不变

- 只要2脚小于基准电压,输出为1,管子截至

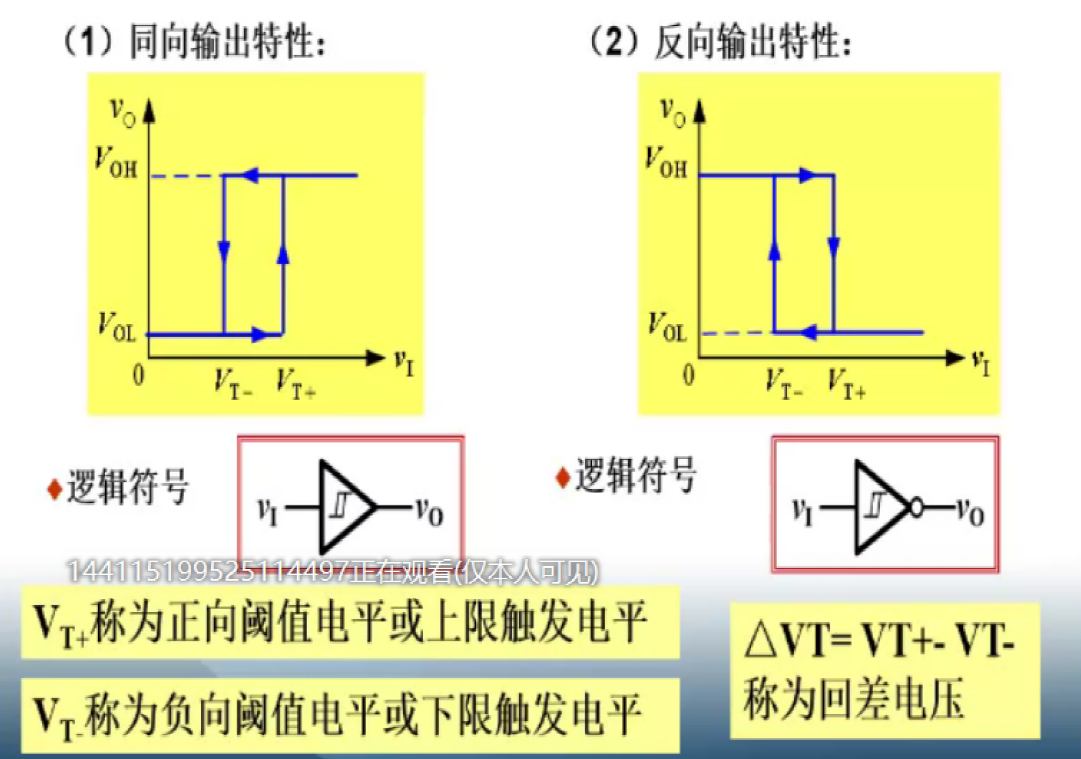

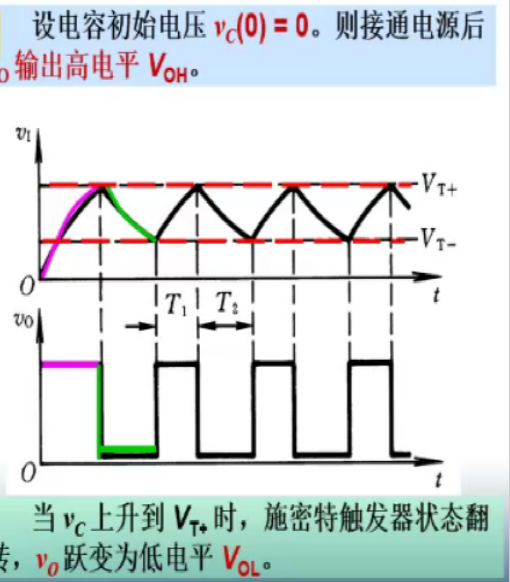

施密特触发电路

传输特性:

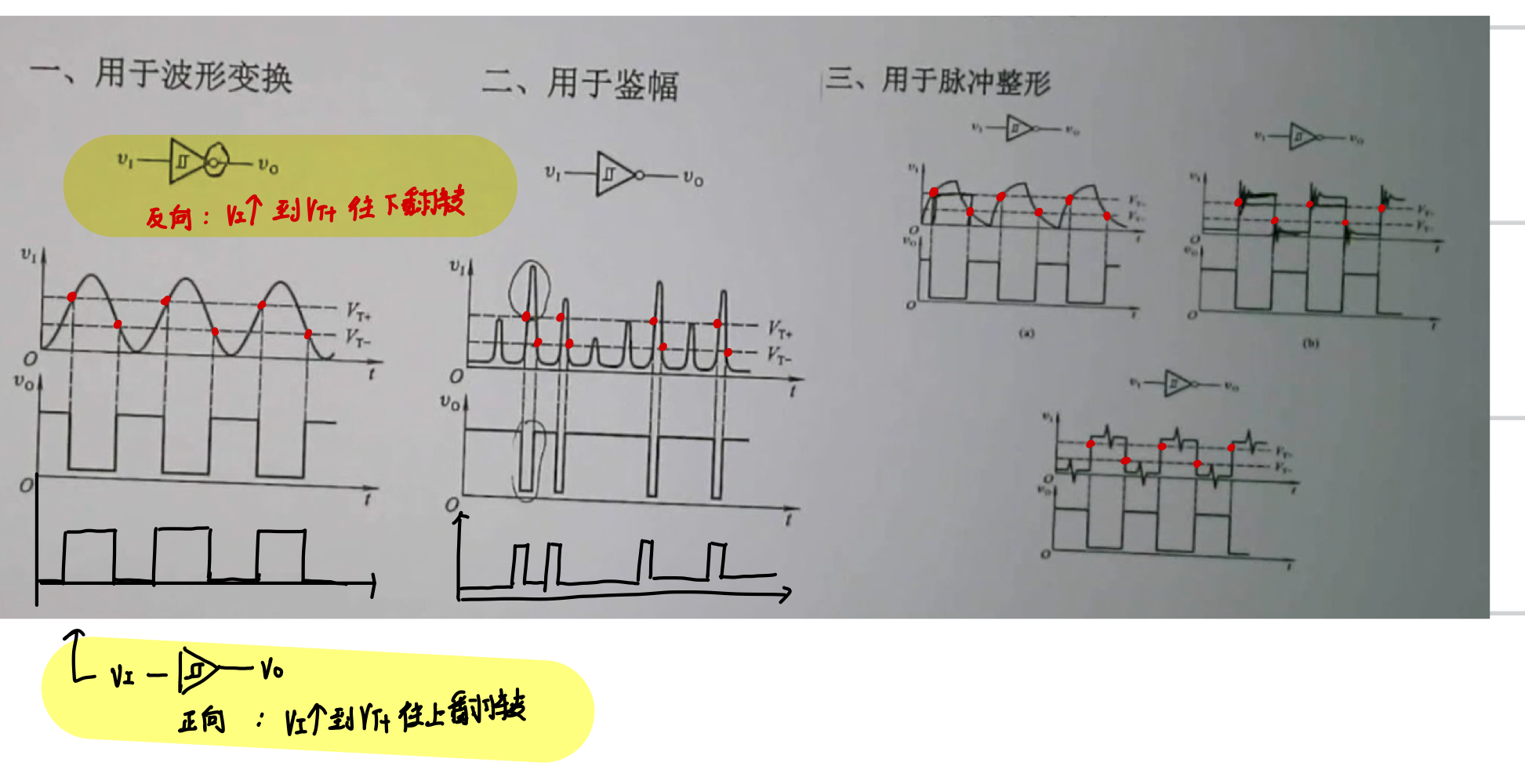

应用-画图:

☆画图口诀:

- 不管是正向还是反向

- 找出起点低于Vt-终点高于Vt+的波形线段,选其与Vt+的交点往下画虚线;找出起点高于Vt+起点低于Vt-的波形线段,选其与Vt-的交点往下画虚线;

- 画一开始的波形,然后遇到虚线就反转(一开始的波形:反向-正波;正向-反波)

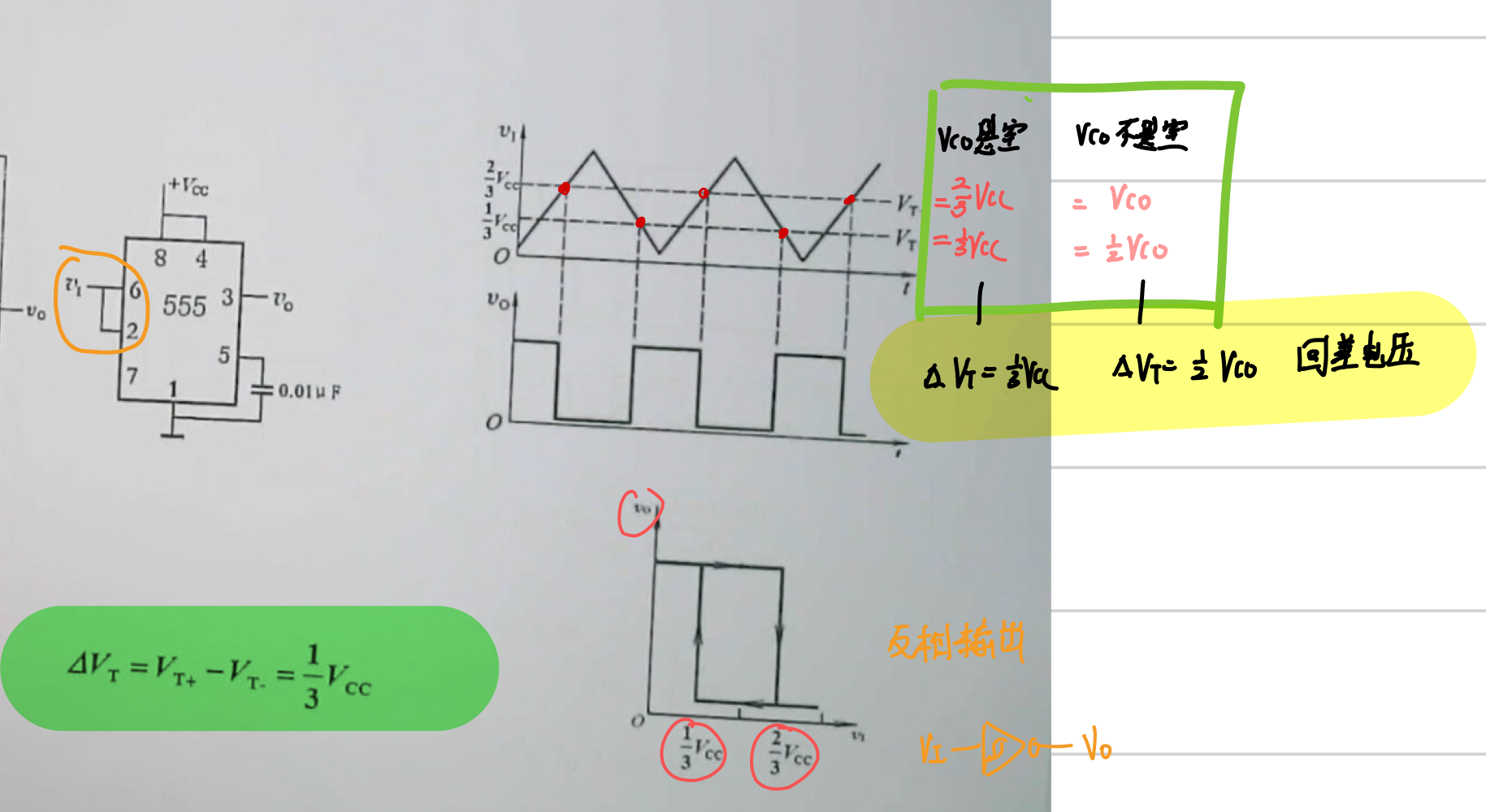

555定时器构成:

构成多谐振荡器

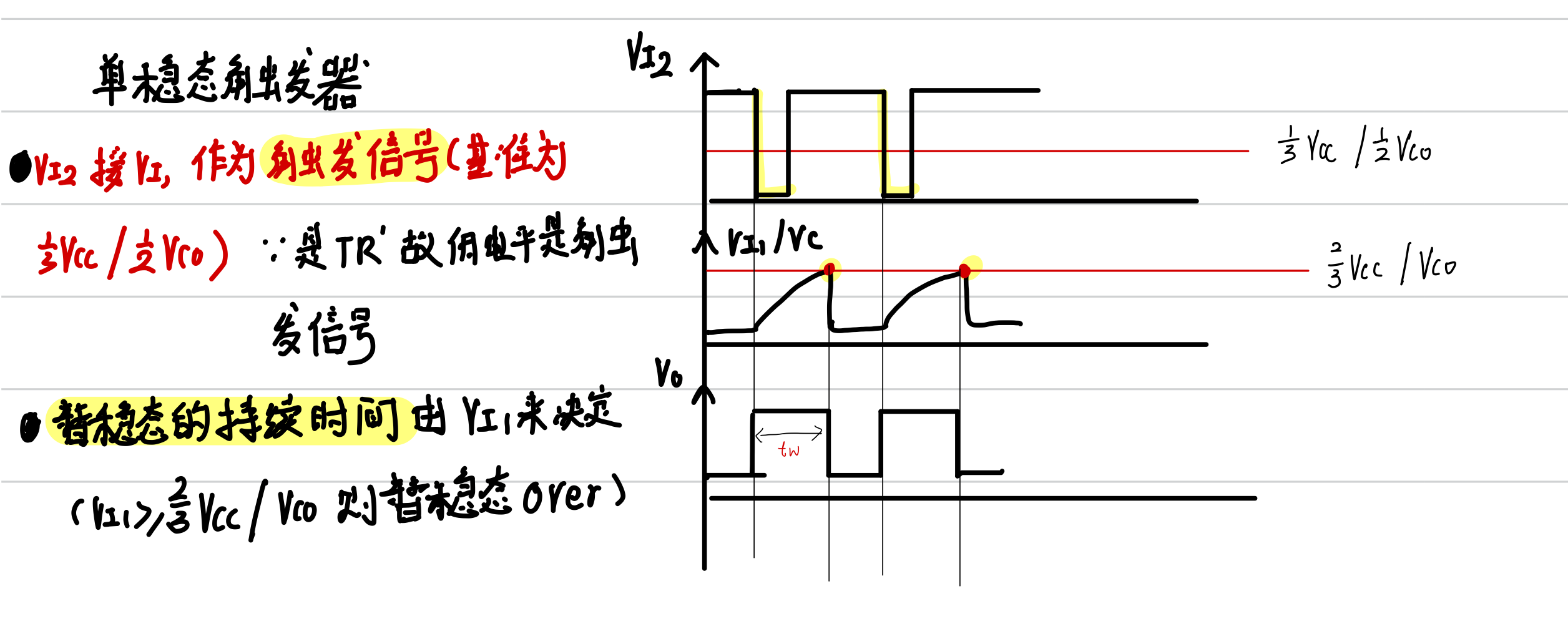

单稳态触发器

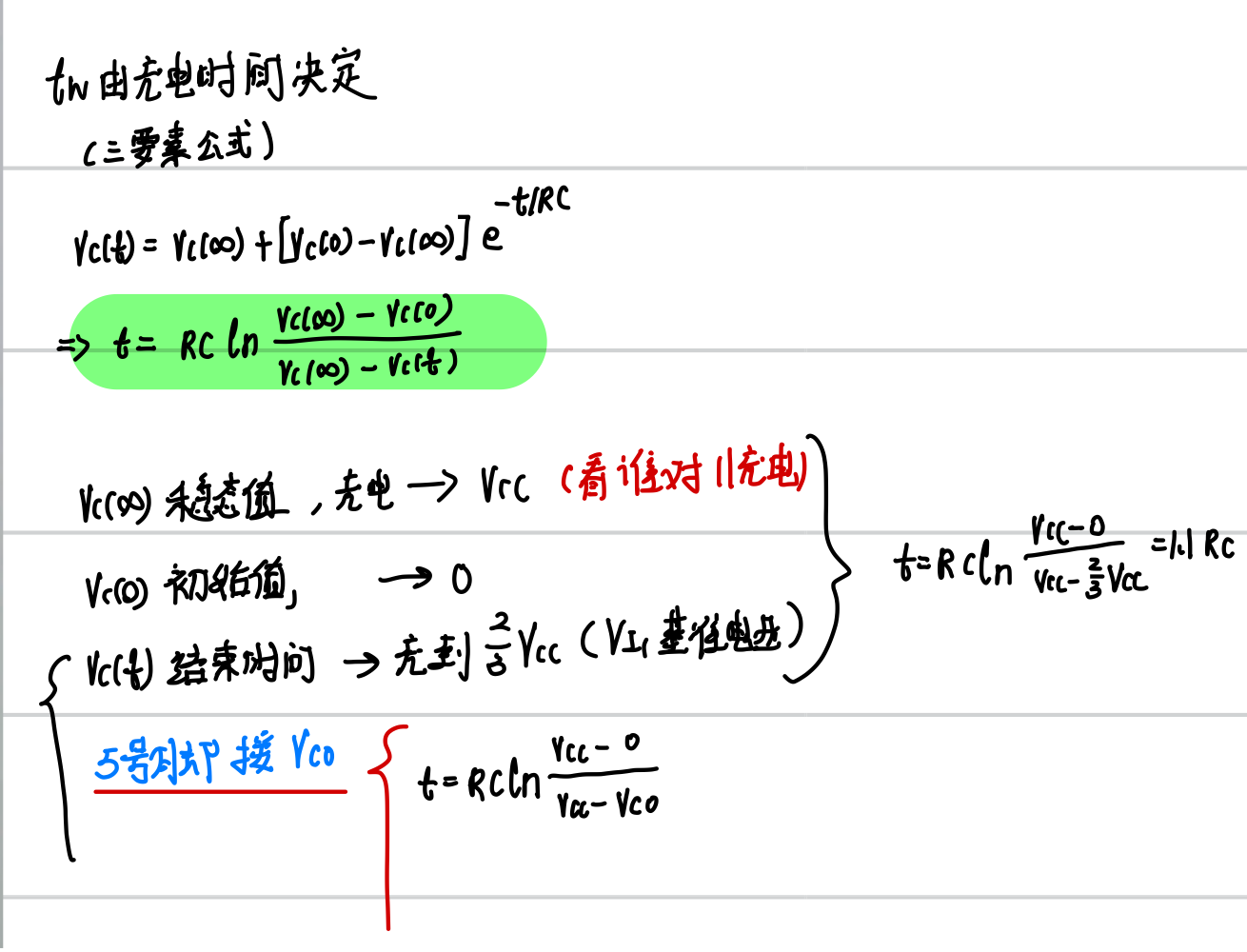

特点:暂稳态的宽度即为输出脉宽,和触发信号无关,只取决于电路内部构造

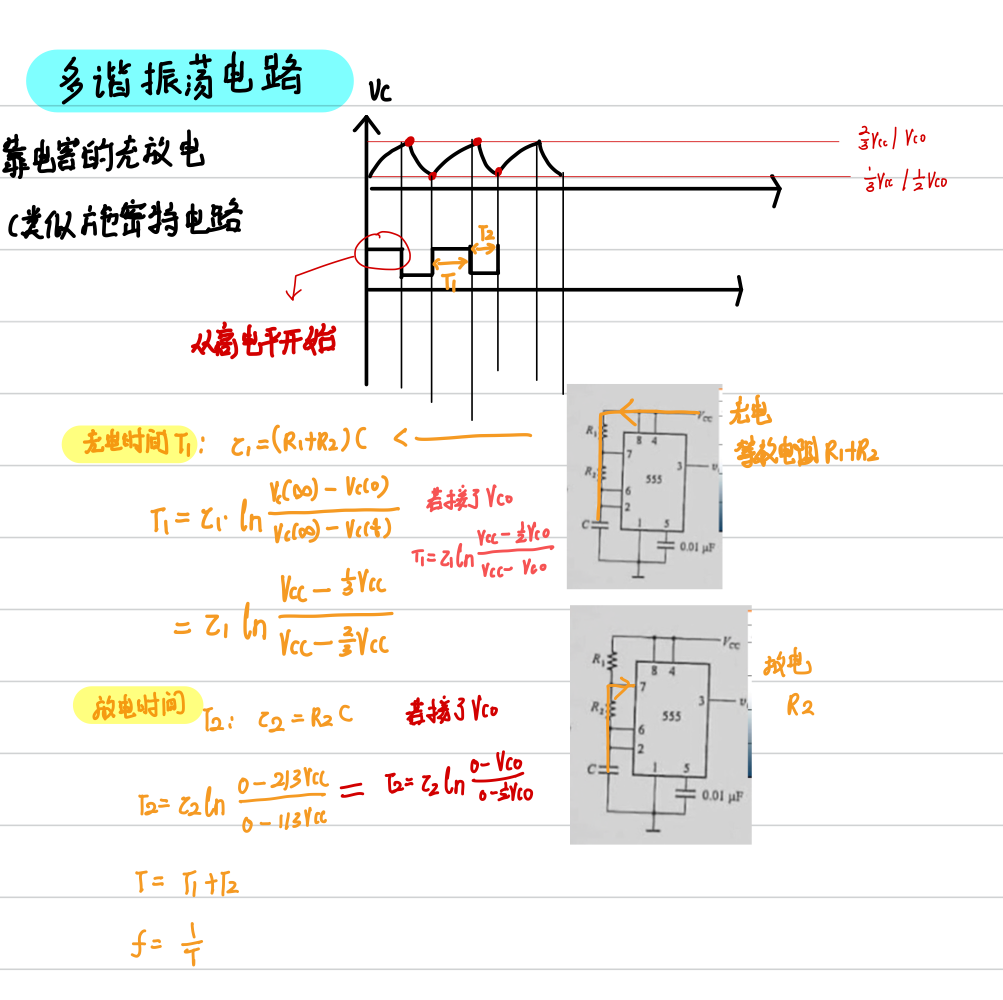

多谐振荡电路

特点:

- 不需要输入信号(2,6脚接在一起没有输入),没有稳定状态,只有两个暂稳态

- 由充放电产生自激振荡,产生周期的矩形波信号

注意变化题型:

- 接了Vco

- 电阻变化