变量的应用(上)

1. 变量值的替换

- 使用指定字符(串)替换变量值中的后缀字符(串)

- 语法格式:(var:a=b)或(var:a=b)或{var:a=b}

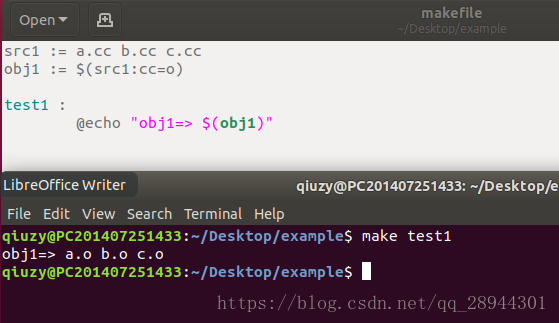

示例1-变量值的替换

src1 := a.cc b.cc c.cc

obj1 := $(src1:cc=o)

test :

@echo "obj1 => $(obj1)"

2. 变量的模式替换

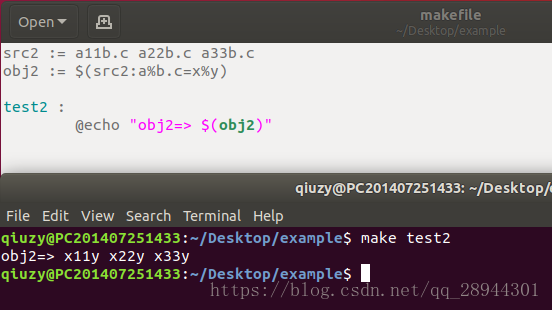

使用%保留变量值中的指定字符,替换其他字符 语法格式:(var:a%b=x%y)或(var:a{var:a%b=x%y} 示例2--变量的模式替换

src2 := a11b.c a22b.c a33b.c

obj2 := $(src2:a%b.c=x%y)

test :

@echo "obj2=> $(obj2)"

注意:

- 替换表达式中不能有任何的空格

- make中支持使用${}对变量进行取值

3. 规则中的模式替换

targets : target-pattern : prereq-pattern

command1

command2

...

说明: 通过target-pattern从targets中匹配子目标;再通过prereq-pattern从子目标生成依赖;从而构成完整的规则。

示例3--规则中的模式替换

OBJS := func.o main.o

$(OBJS) : %.o : %.c

gcc -o $@ -c $^

等价于

OBJS := func.o main.o

func.o : func.c

gcc -o $@ -c $^

main.o : main.c

gcc -o $@ -c $^

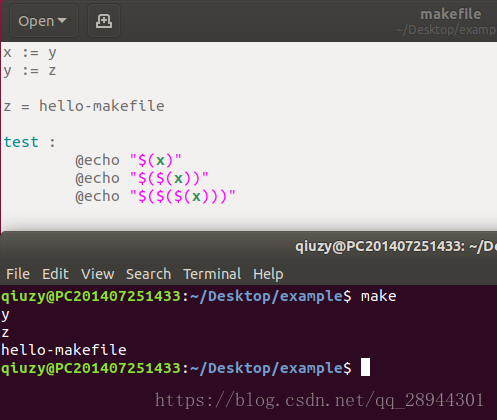

4. 变量值的嵌套引用

- 一个变量名之中可以包含对其他变量的引用

- 嵌套引用的本质是使用一个变量表示另外一个变量 示例4--变量值的嵌套引用

x := y

y := z

z := hello-makefile

test :

@echo "$(x)"

@echo "$($(x))"

@echo "$($($(x)))"

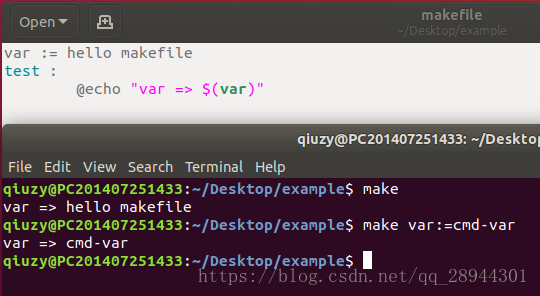

5. 命令行变量

- 运行make时,再命令行定义变量

- 命令行变量默认覆盖makefile中定义的变量 示例5--命令行变量

var := hello makefile

test :

@echo "var => $(var)"

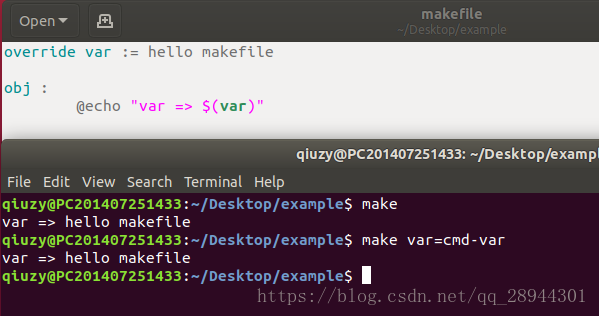

6. override关键字

- 用于指示makefile中定义的变量不能被覆盖

- 变量的定义和赋值都需要使用override关键字 示例6--override关键字

override var := hello makefile

obj:

@echo "var => $(var)"

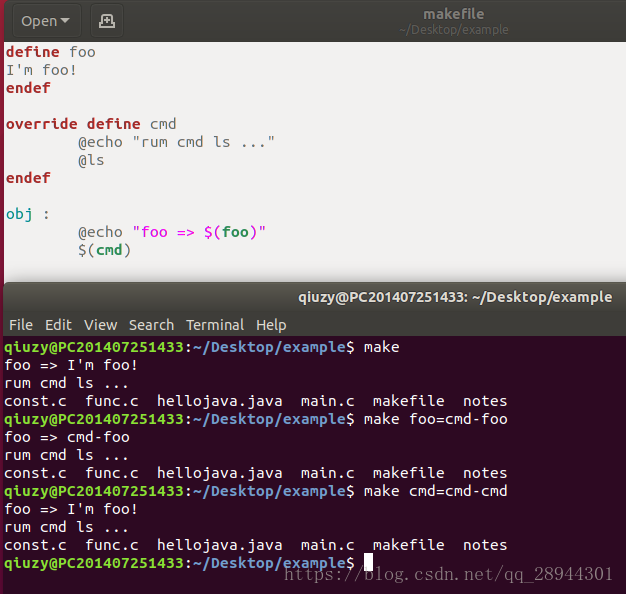

7. define关键字

- 用于在makefile中定义多行变量

- 多行变量的定义从变量名开始到endef结束

- 可使用override关键字防止变量被覆盖

- define定义的变量等价于使用=定义的变量 示例7--define关键字

define foo

I'm foo!

endef

override define cmd

@echo "run cmd ls ..."

@ls

endef

test :

@echo "foo => $(foo)"

$(cmd)

小结:

- 变量值的替换:(var:a=b)或(var:a=b)或{var:a=b}

- 变量的模式替换:

{var:a%b=x%y}

- makefile支持将模式替换可以直接用于规则中

- makefile中的变量值能够嵌套引用

- 命令行中定义的变量能够覆盖makefile中定义的变量

- override用于指示makefile中定义的变量不能被覆盖

- define用于在makefile中定义值为多行的变量